# Looking Beyond Microarchitectural-Only Side Channels

#### Mengjia Yan

mengjia@csail.mit.edu

http://people.csail.mit.edu/mengjia/

CRC Seminar Talk October 20, 2022

#### Meltdown & Spectre on the Headlines in 2018

# Meltdown and Spectre: 'worst ever' CPU bugs affect virtually all computers

Everything from smartphones and PCs to cloud computing affected by major security flaw found in Intel and other processors – and fix could slow devices.

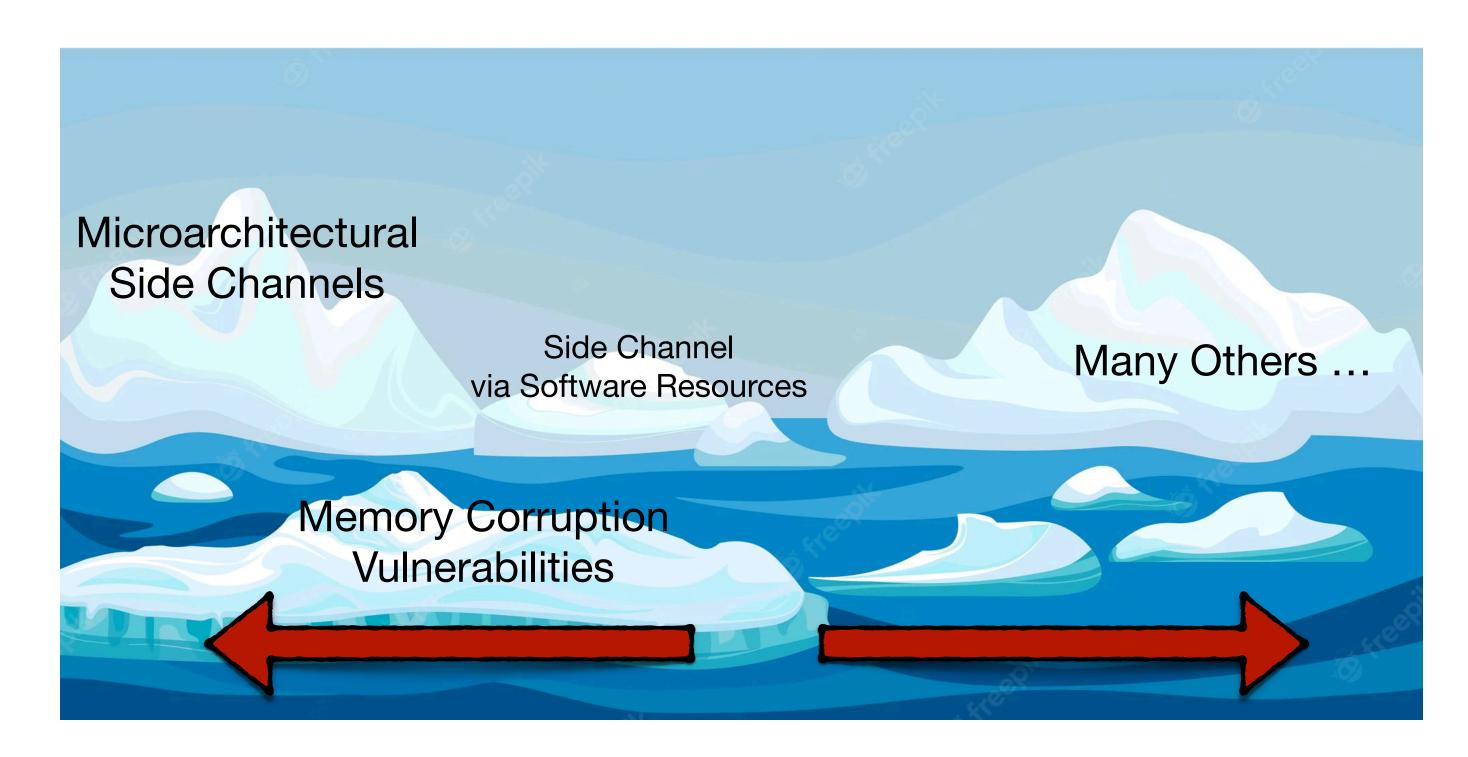

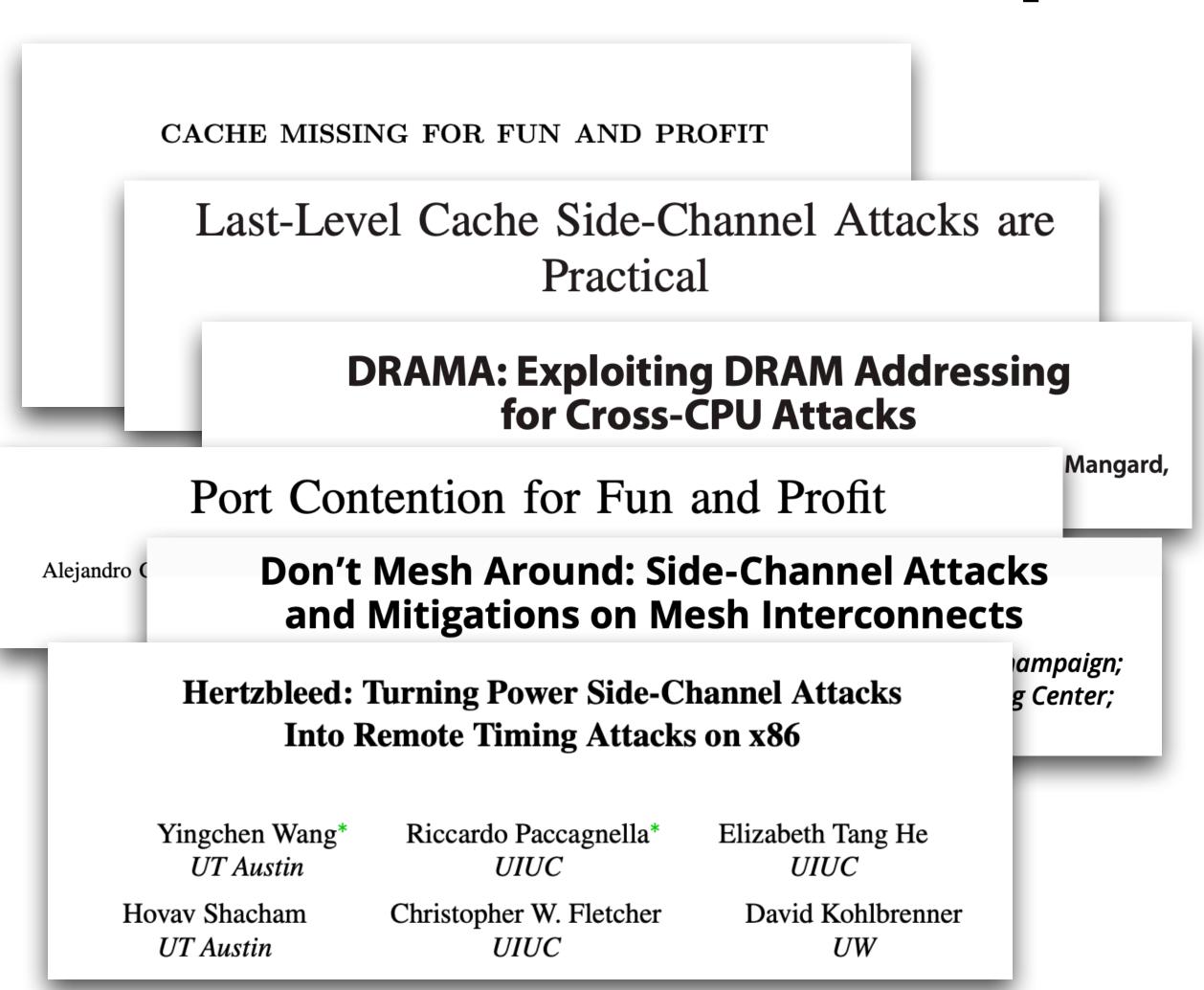

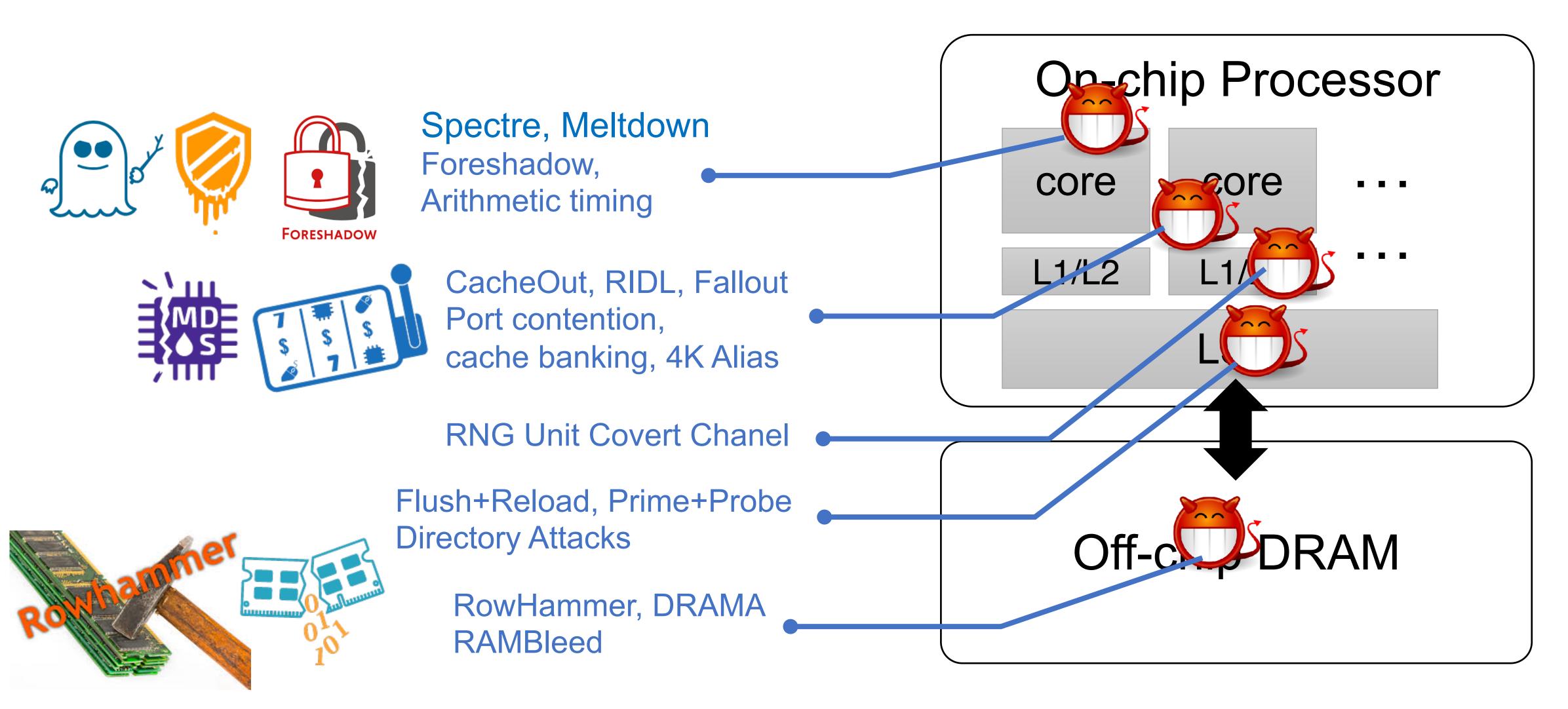

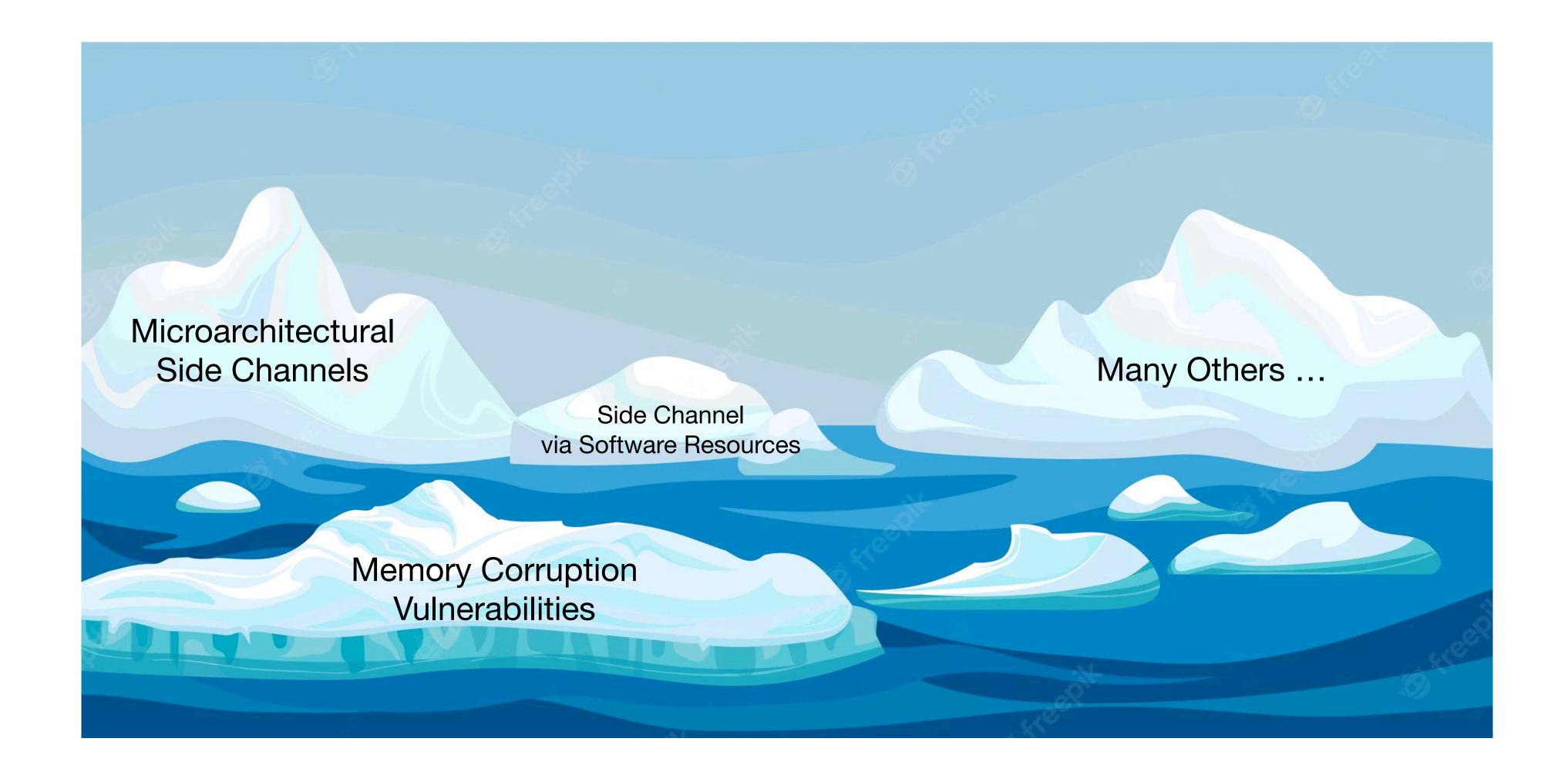

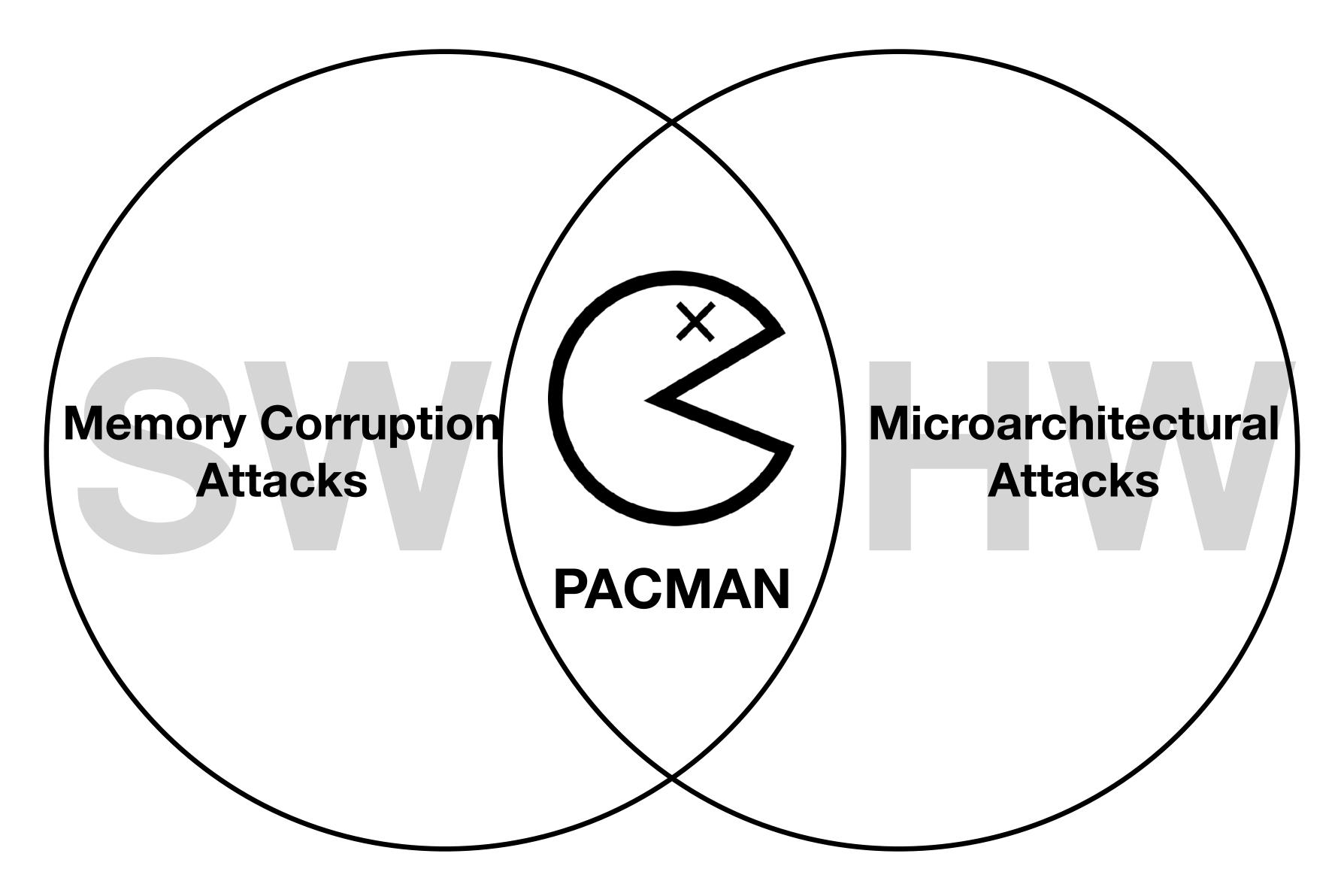

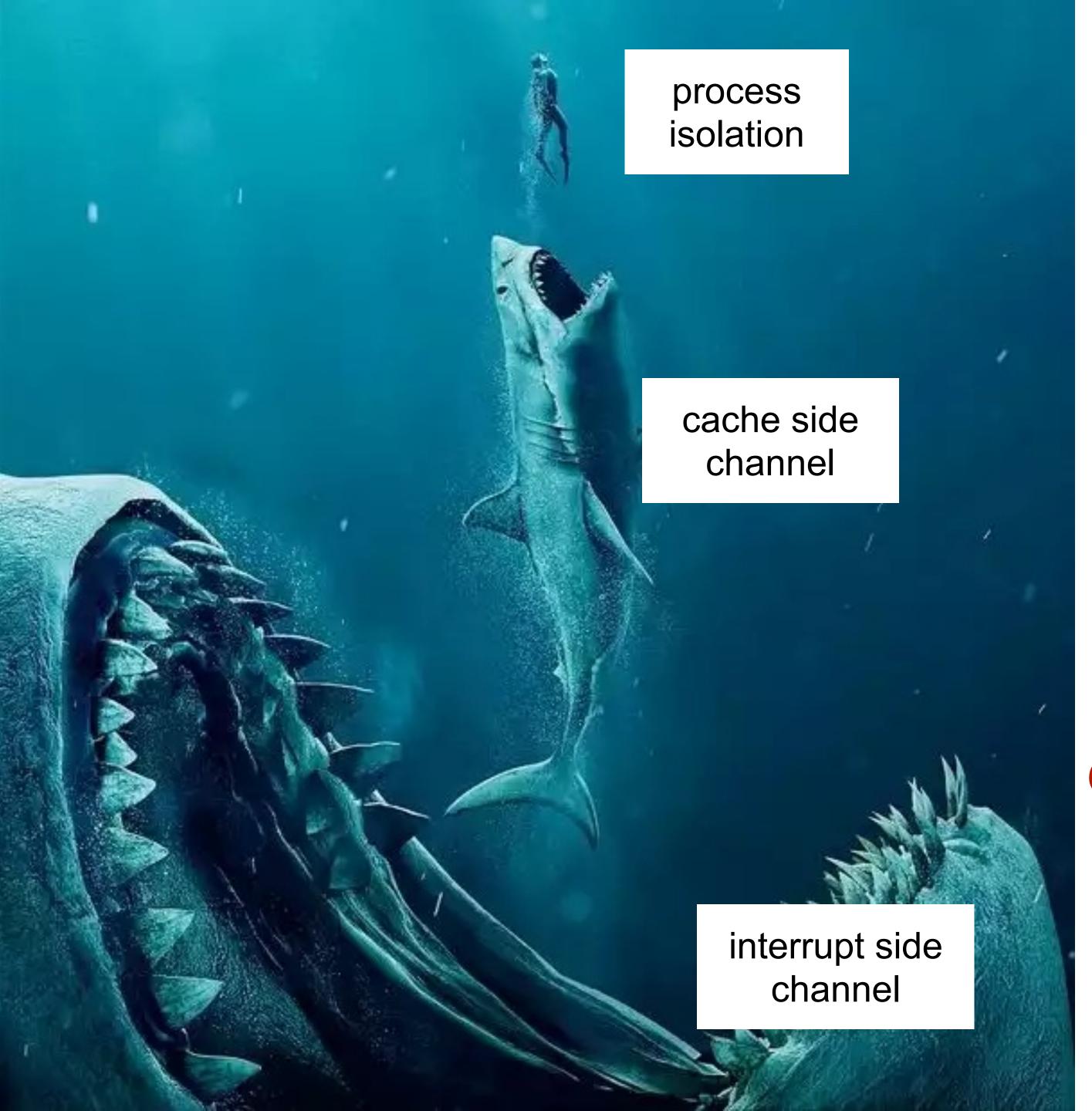

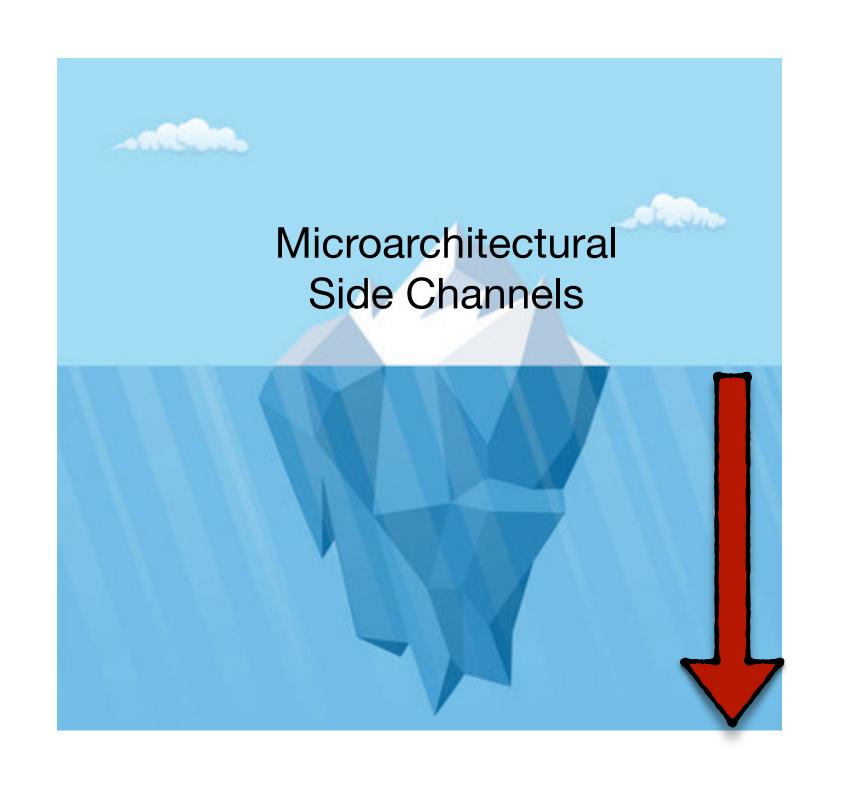

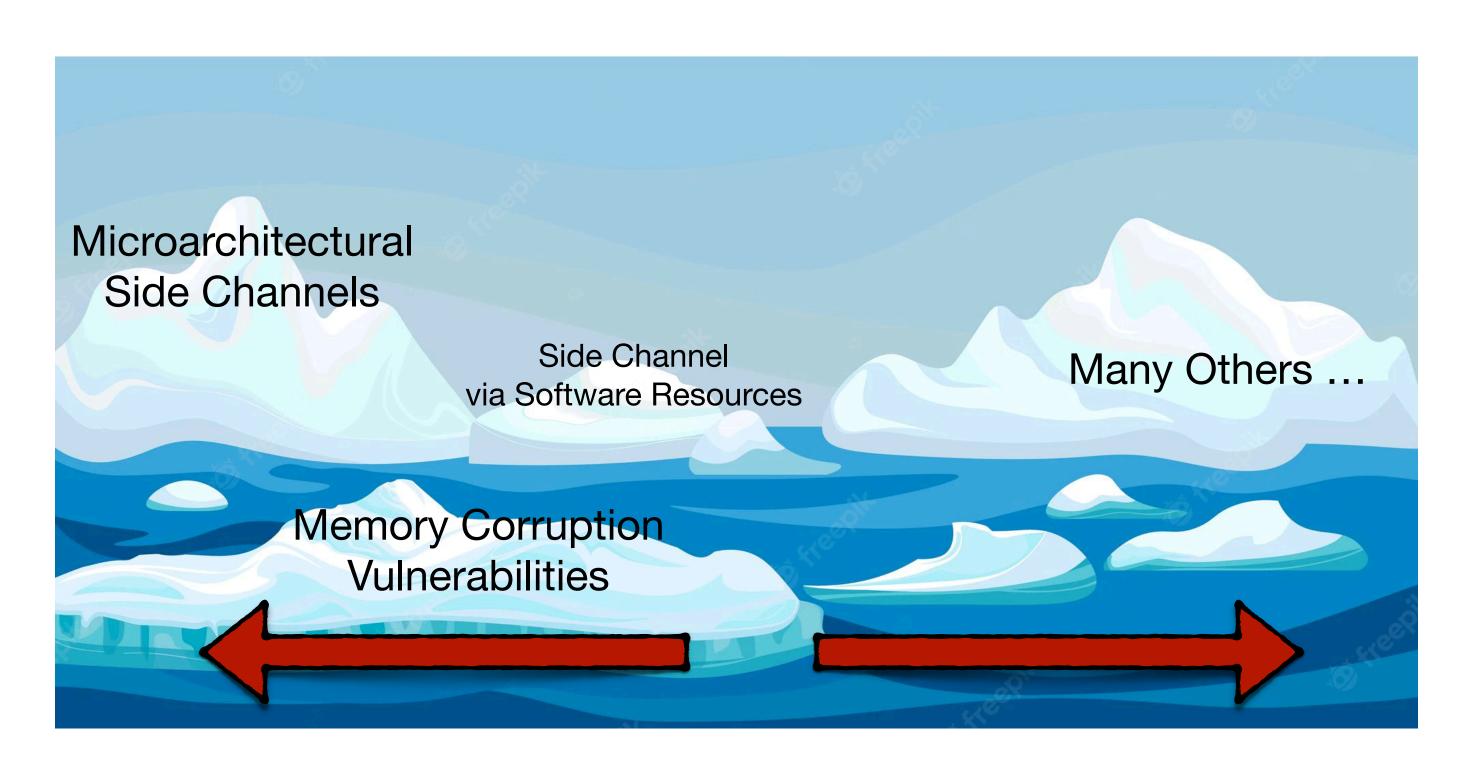

# Current Side Channel Research Landscape

# The Age of Pervasive Hardware Attacks

## However...

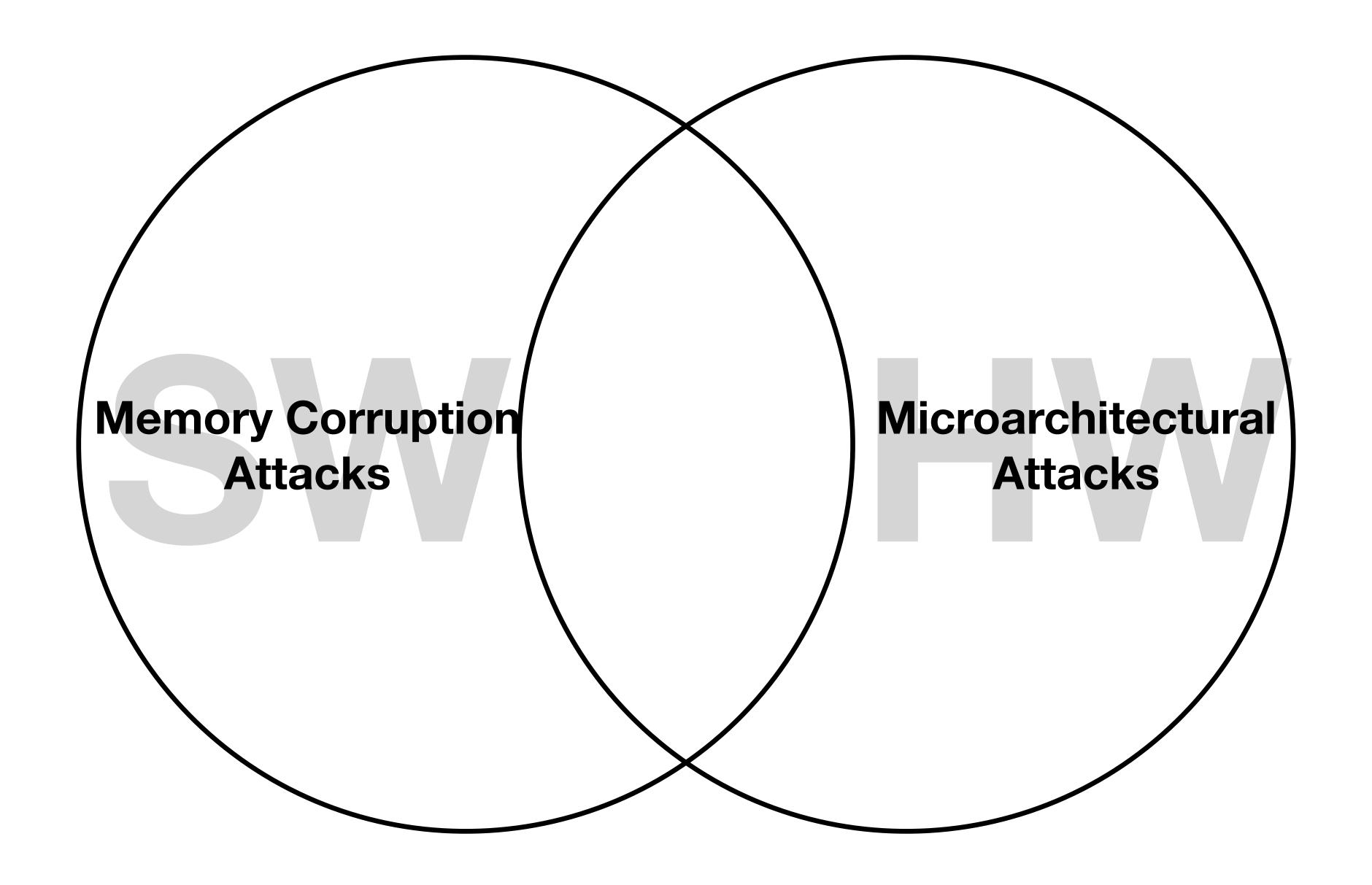

# Limitations of Looking At Microarchitectural-only Side Channels

- Part 1: Miss threats that arise from compound threat models

- Part 2: Misunderstand root causes of existing side channel attacks

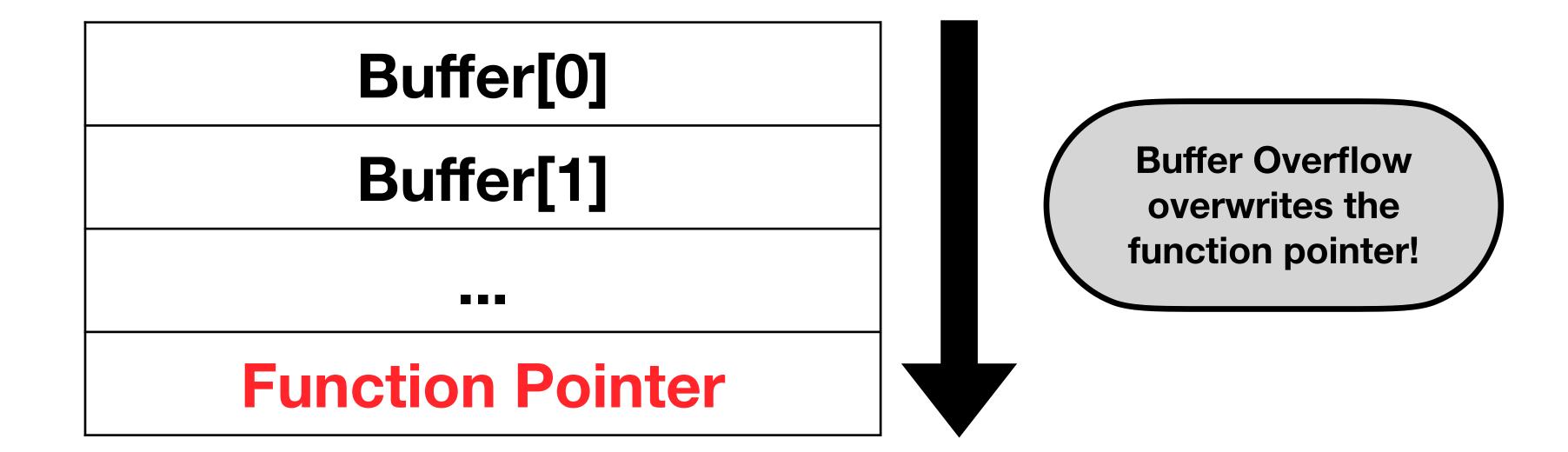

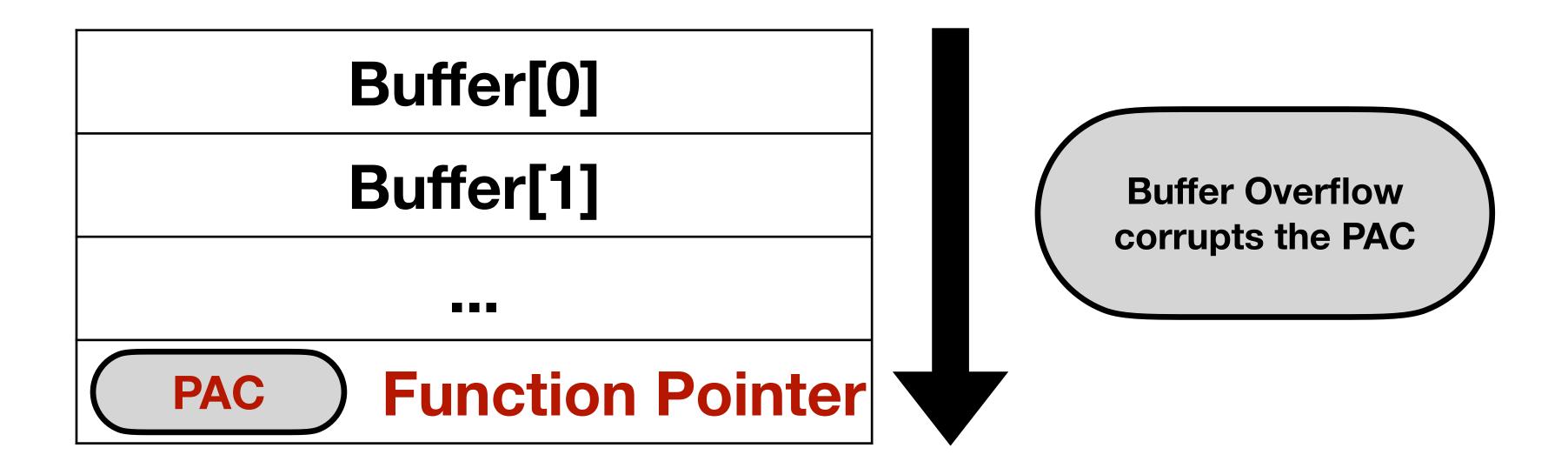

#### Buffer Overflow

Buffer[0]

Buffer[1]

...

Function Pointer

#### Buffer Overflow

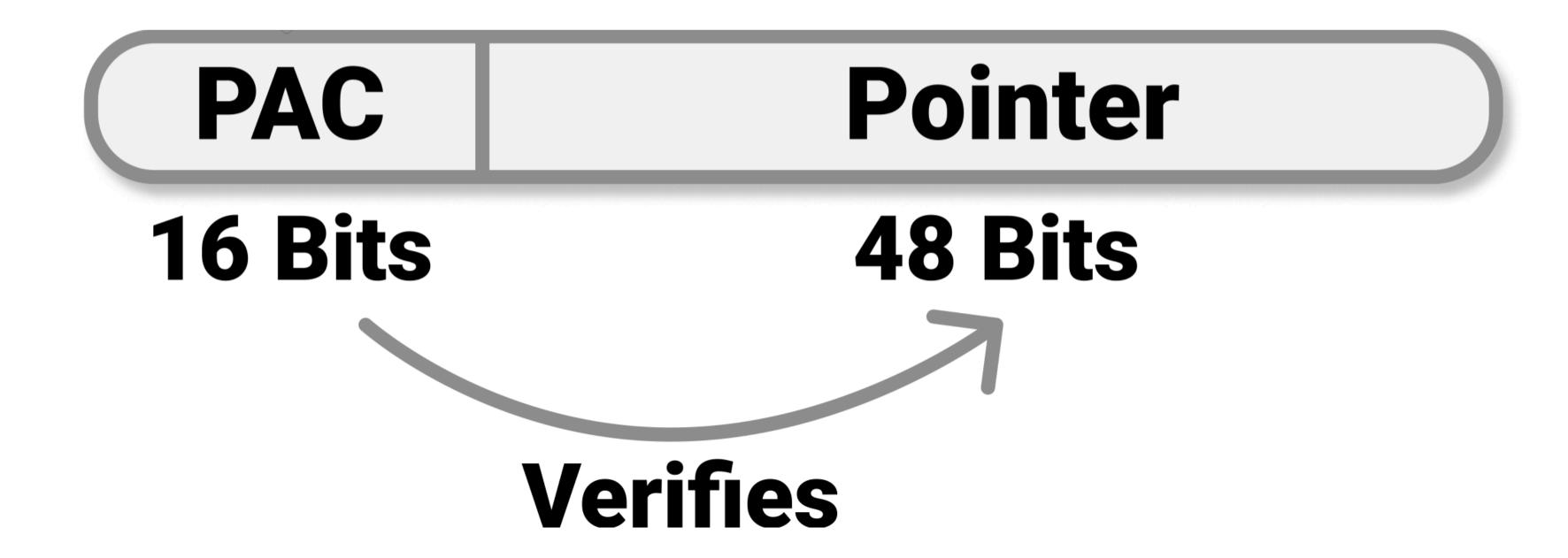

#### **ARM Pointer Authentication**

PAC = crypto\_func(pointer, salt, key)

# Two Operations

# Sign

Before saving a pointer to memory, compute the PAC

### Verify

Before using a pointer, check the pointer's PAC

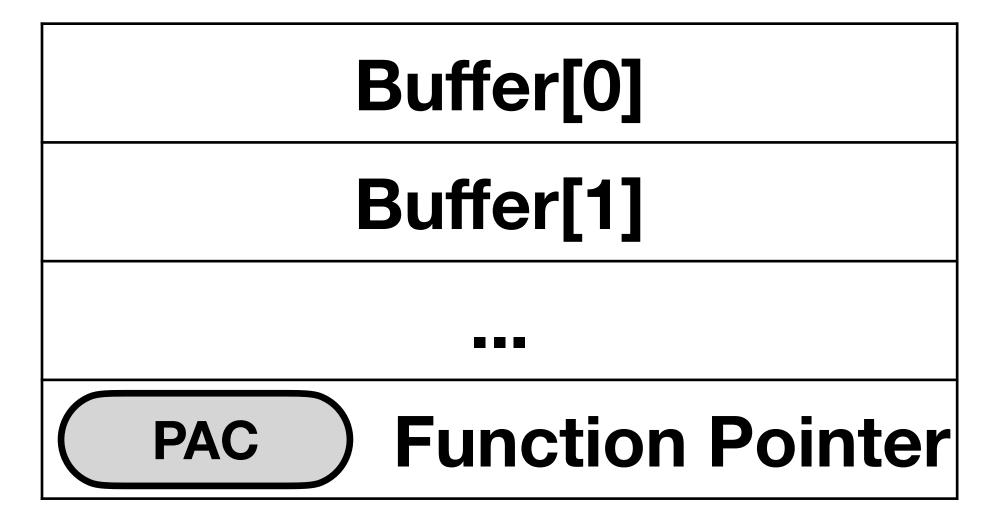

#### Buffer Overflow

#### Buffer Overflow

#### Invalid PAC means we crash!

## **Extending ARM Pointer Authentication**

#### PAC it up: Towards Pointer Integrity using ARM Pointer Authentication

Hans Liljestrand, Aalto University, Huawei Technologies Oy; Thomas Nyman, Aalto University: Kui Wana Huawei Technologies Oy Tampere University of Technologies

Ca

#### PTAuth: Temporal Memory Safety via Robust Points-to Authentication

Reza Mirzazade Farkhani, Mansour Ahmadi, and Long Lu, Northeastern

# Protecting Indirect Branches against Fault Attacks using ARM Pointer Authentication

Pascal Nasahl

Graz University of Technology

pascal.nasahl@iaik.tugraz.at

Robert Schilling

Graz University of Technology

robert.schilling@iaik.tugraz.at

Stefan Mangard

Graz University of Technology

Lamarr Security Research

stefan.mangard@iaik.tugraz.at

#### Hardware-based Always-On Heap Memory Safety

Yonghae Kim

Georgia Institute of Technology

yonghae@gatech.edu

Jaekyu Lee

Arm Research

jaekyu.lee@arm.com

Hyesoon Kim

Georgia Institute of Technology

hyesoon@cc.gatech.edu

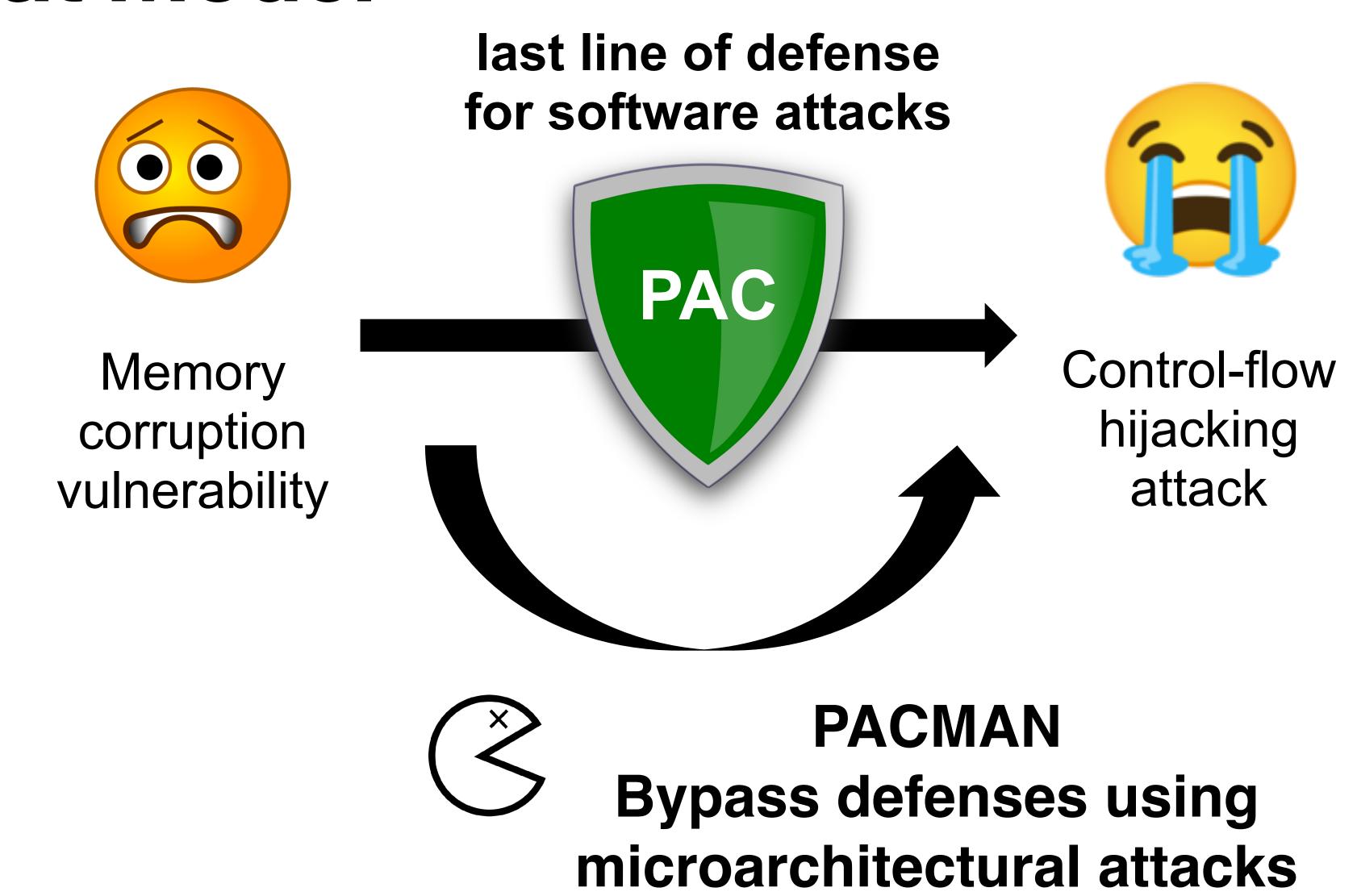

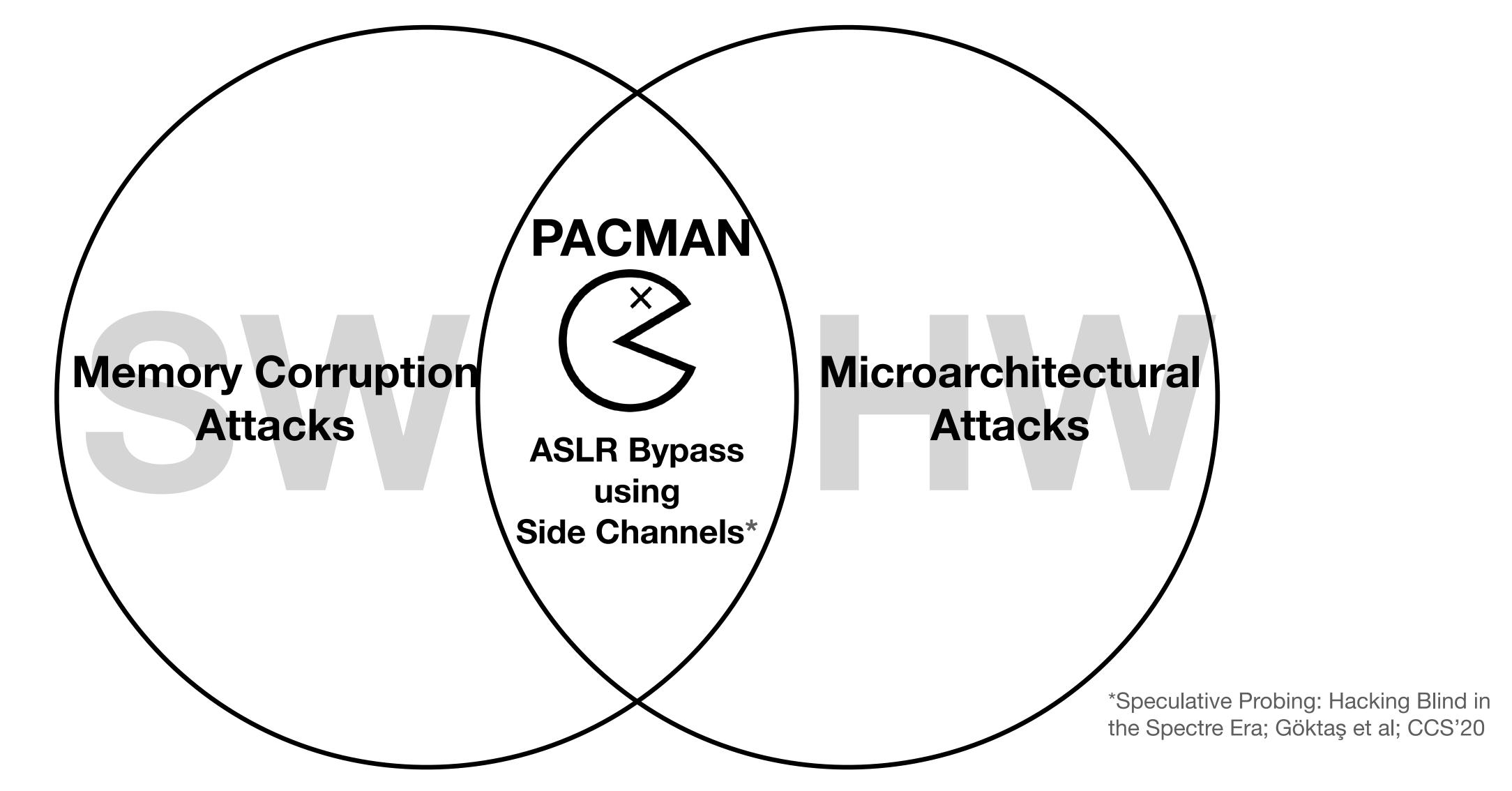

The security properties of these mechanisms have been examined **solely** under the memory safety threat model.

#### **Threat Model**

# Key Insight

#### **Break PAC with Microarchitectural Attacks**

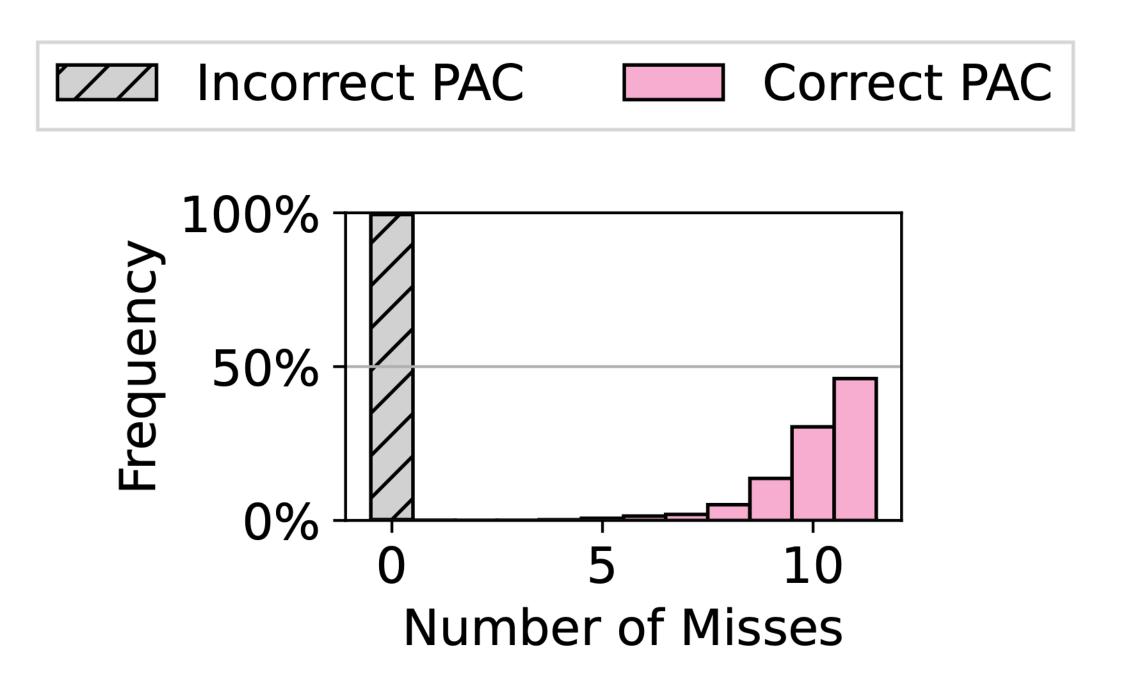

- 1. Guess a PAC speculatively to prevent crashes

- 2. Leak verification results via side channel

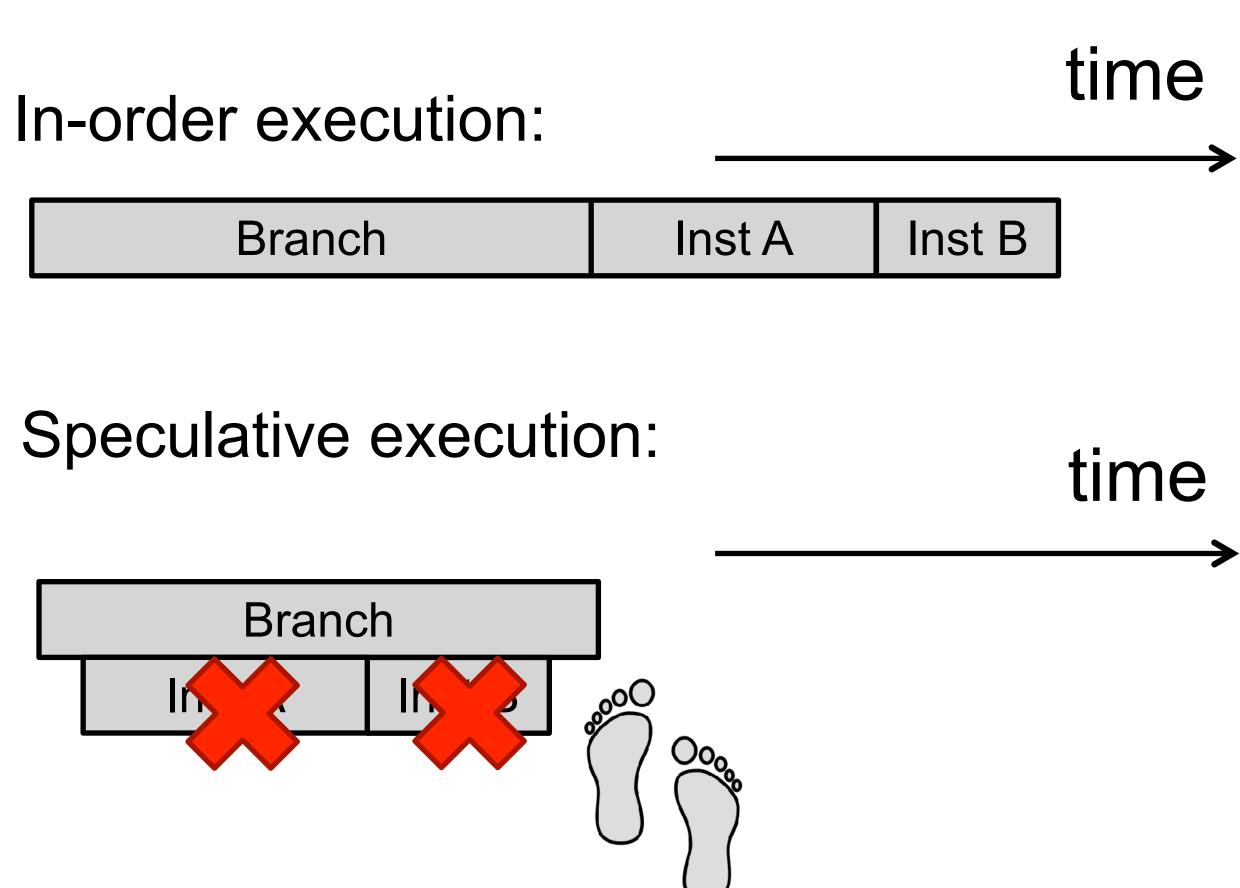

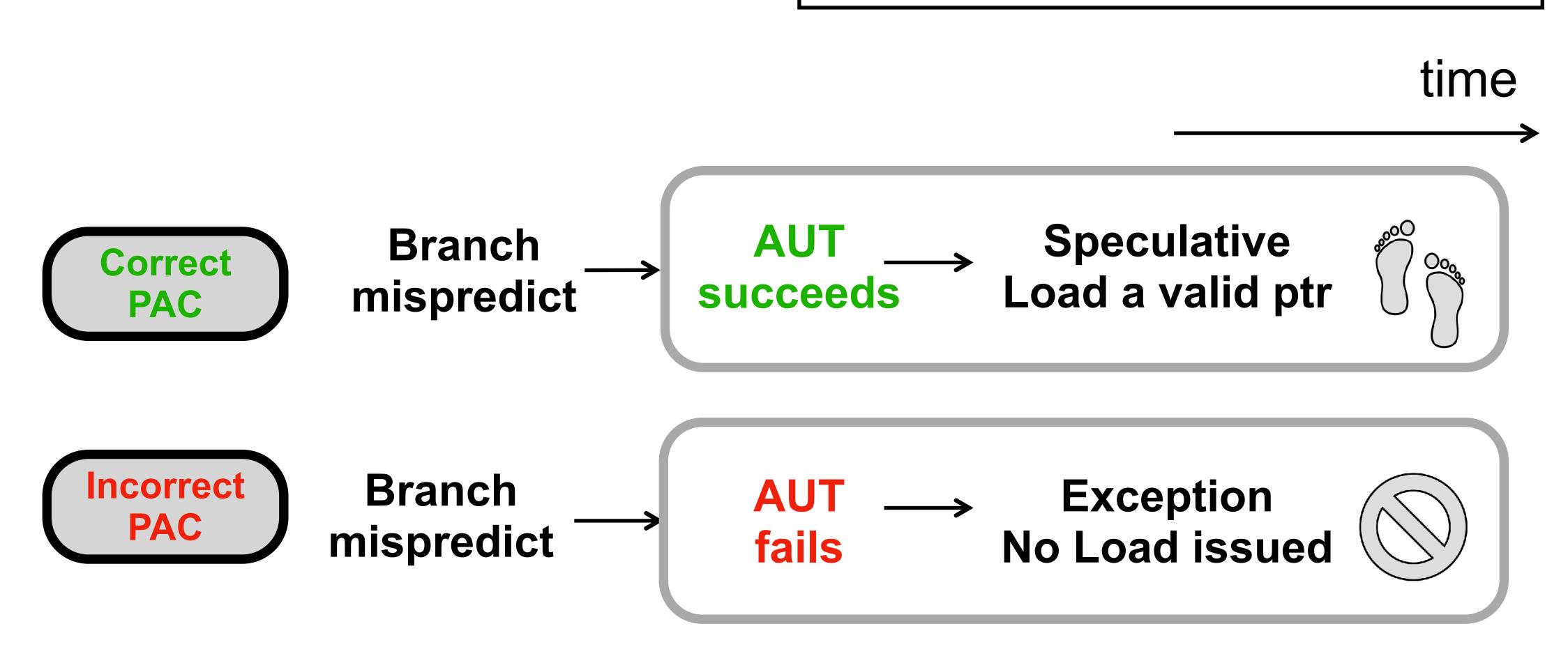

## Speculative Execution

```

if (...) { //Branch

Inst A

Inst B

}

```

Micro-architecture side effects are not rolled back

# PACMAN Gadgets

```

if (condition):

verified_ptr = AUT(guess_ptr) // AUT

load(verified_ptr) // LD

```

**Data Gadget**

#### Attack Procedure

```

if (condition):

verified_ptr = AUT(guess_ptr) // AUT

load(verified_ptr) // LD

```

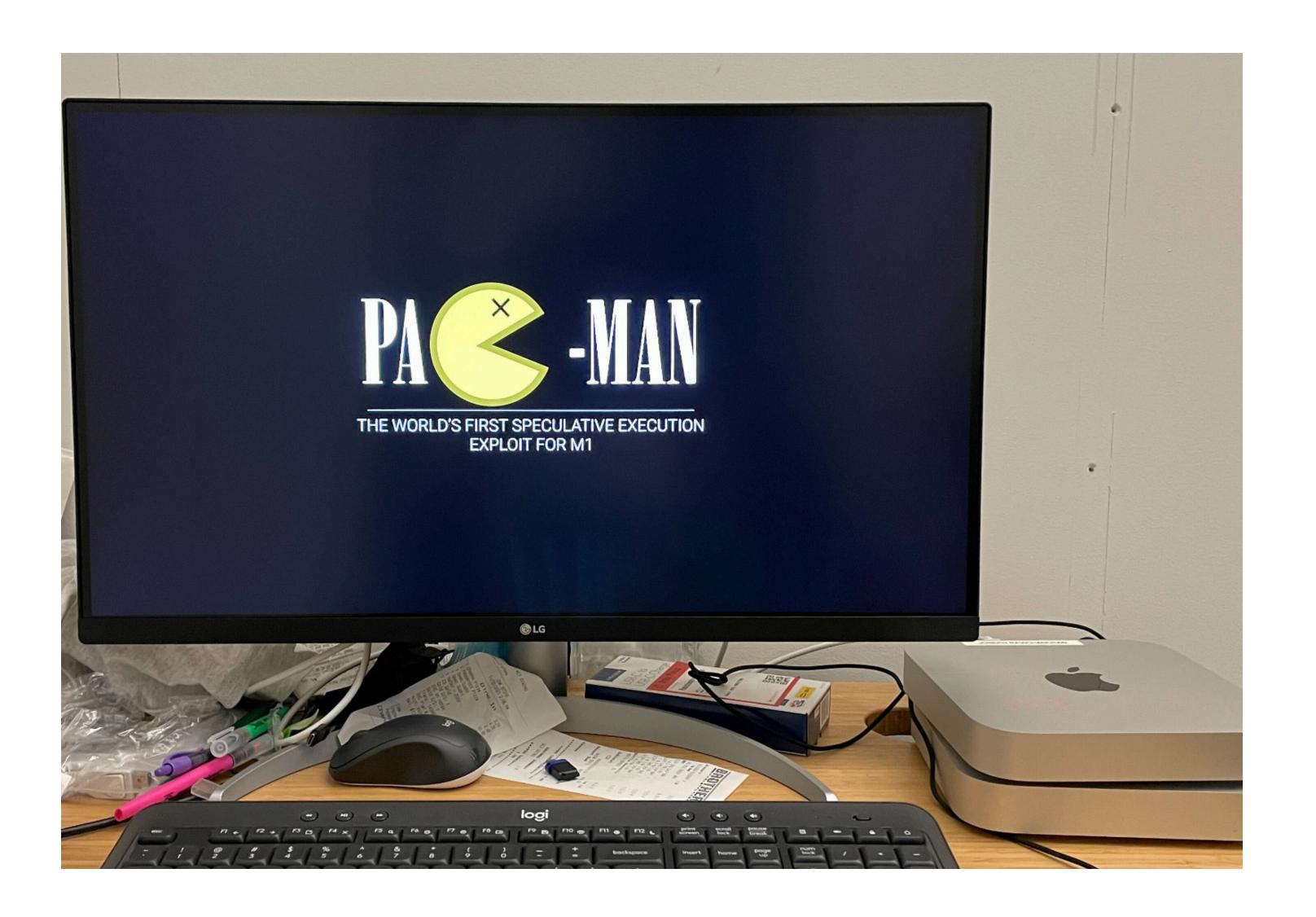

#### TARGET

The world's first desktop CPU that supports Pointer Authentication.

Image: Apple ("Apple Unleashes M1")

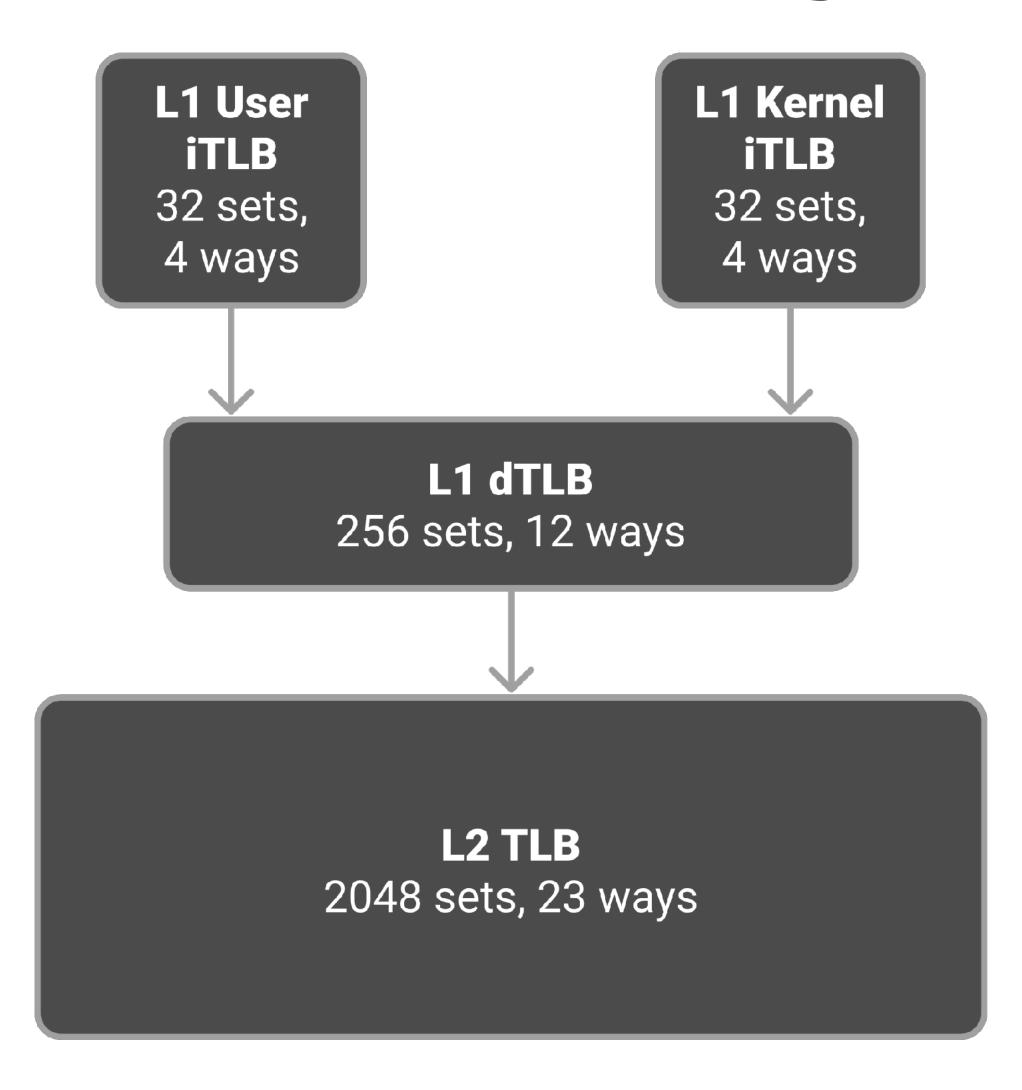

## Challenges of Real World Hardware

- No documentation of microarchitectural details.

- No high resolution timer.

- macOS is a difficult system to integrate attacks on.

Essentially, we had to reinvent the wheel.

# Conjectured TLB Hierarchy

## PAC Oracle Accuracy

With a highly reliable PAC oracle, the attacker can brute-force the PAC value.

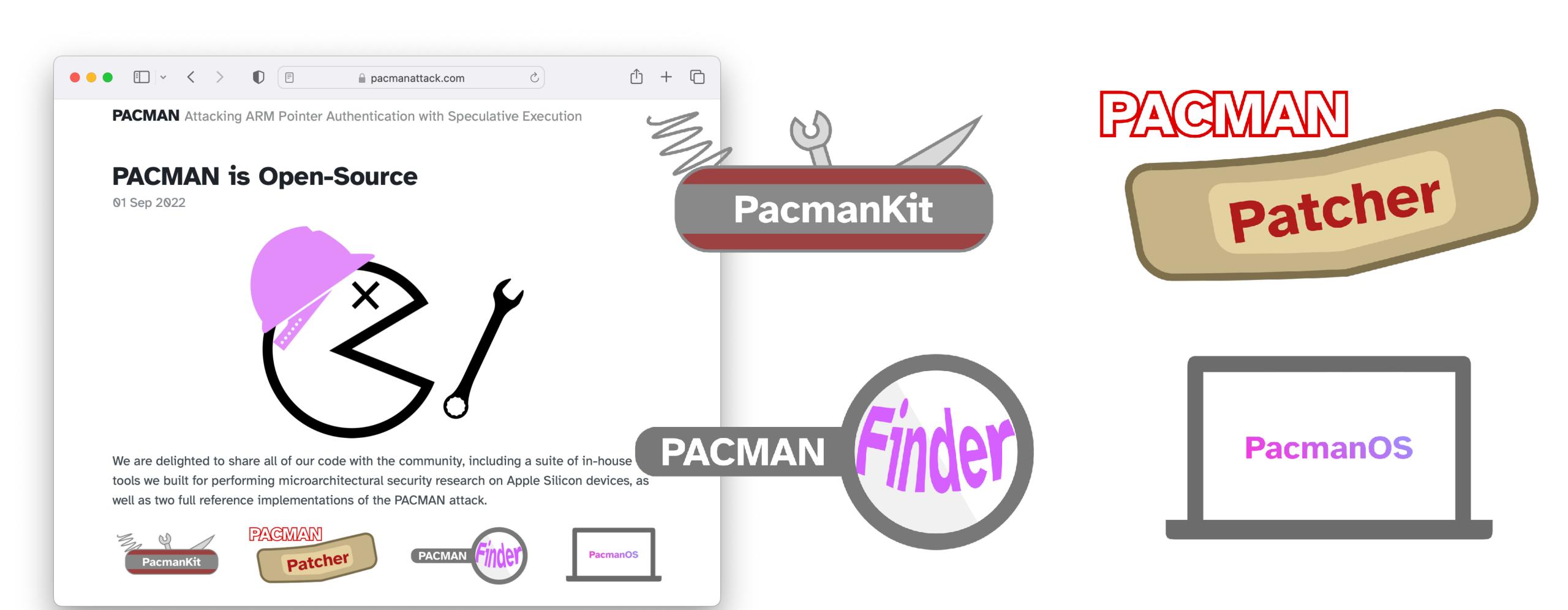

#### PacmanOS

A Rust-based bare metal environment for performing experiments.

#### PACMAN @DEFCON

Takeaway 1: New threats arise from compound threat models

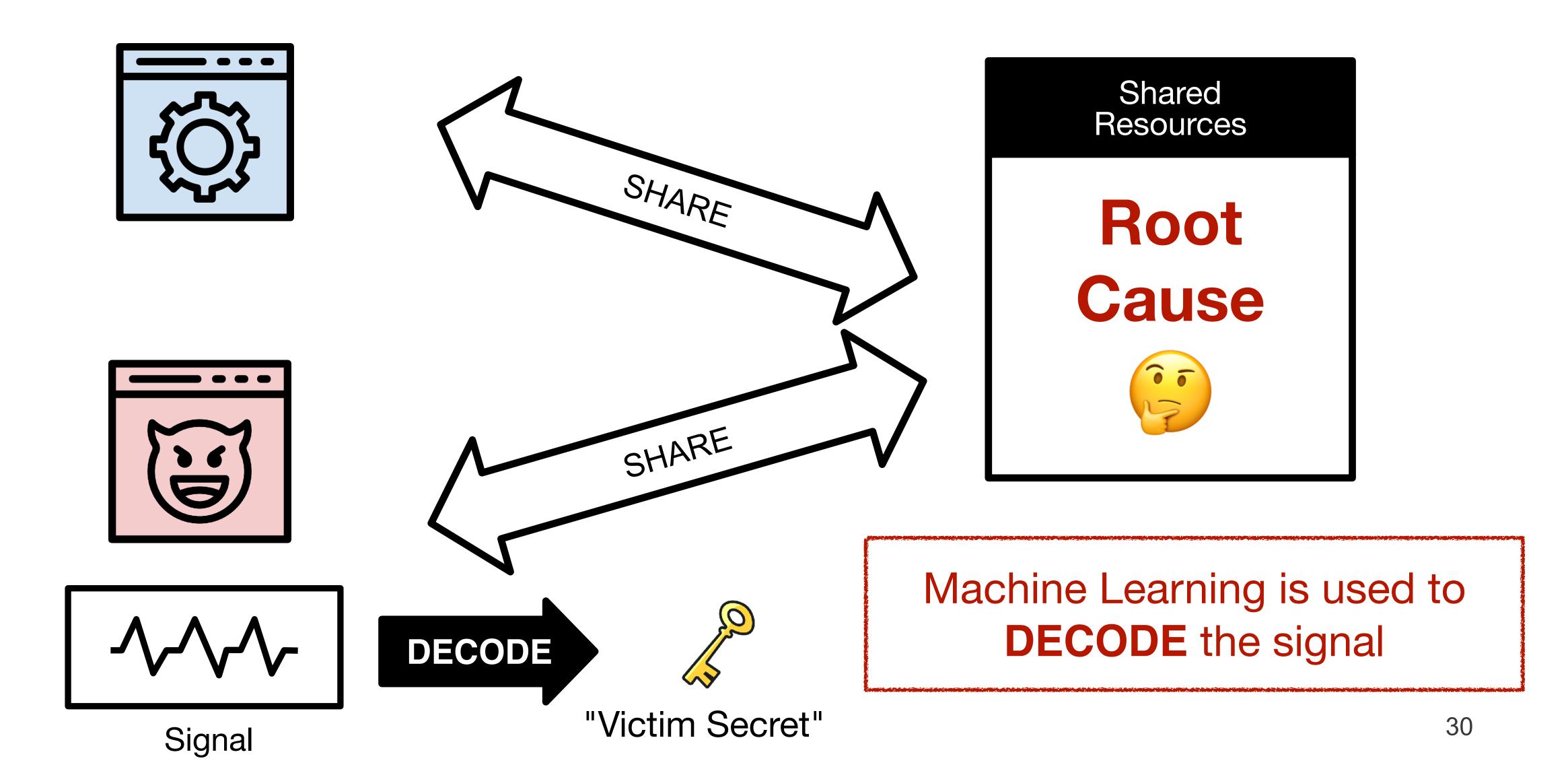

# Limitations of Looking At Microarchitectural-only Side Channels

- Part 1: Miss threats that arise from compound threat models

- Part 2: Misunderstand root causes of existing side channel attacks

#### Microarchitectural Timing Side Channels

#### Microarchitectural Timing Side Channels

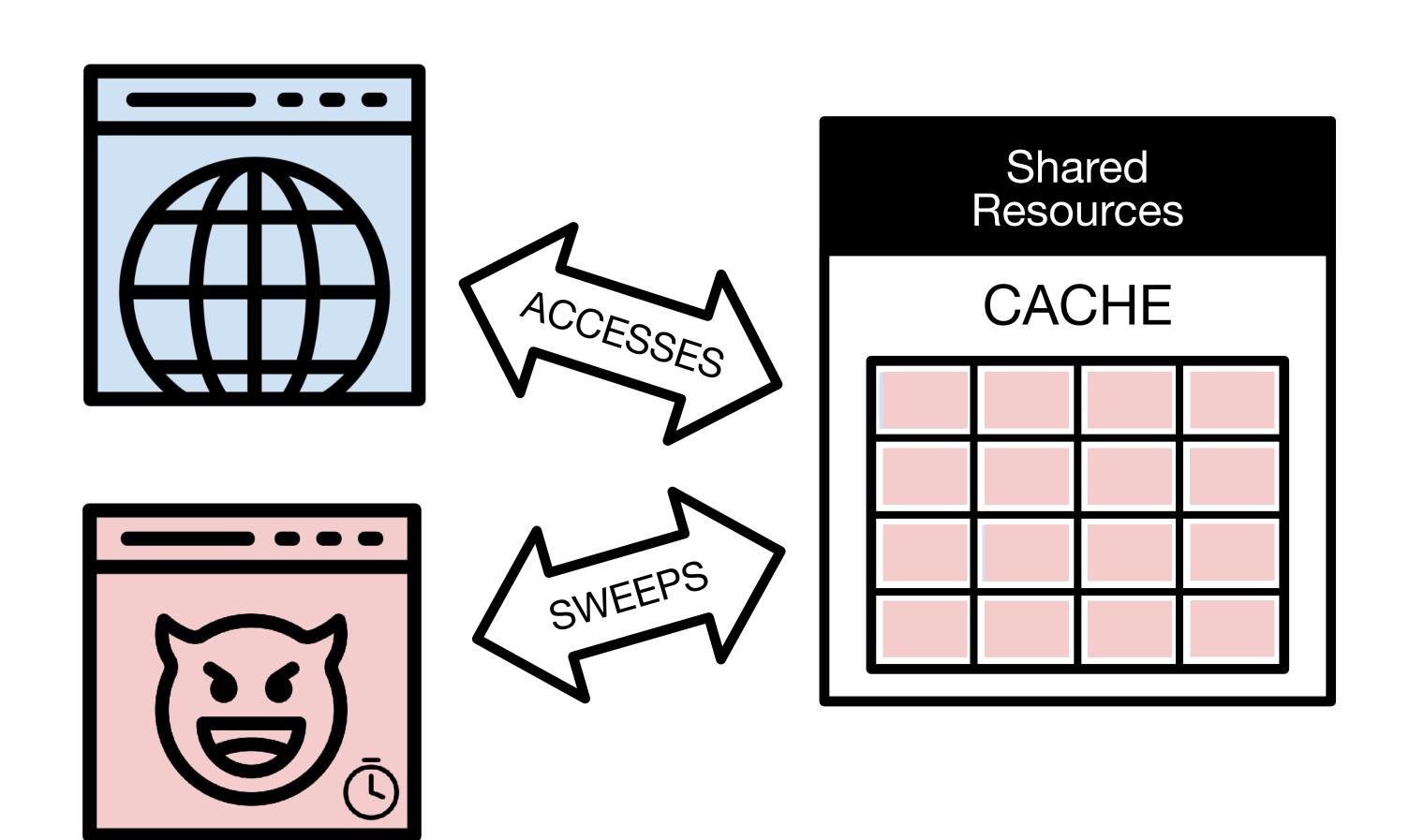

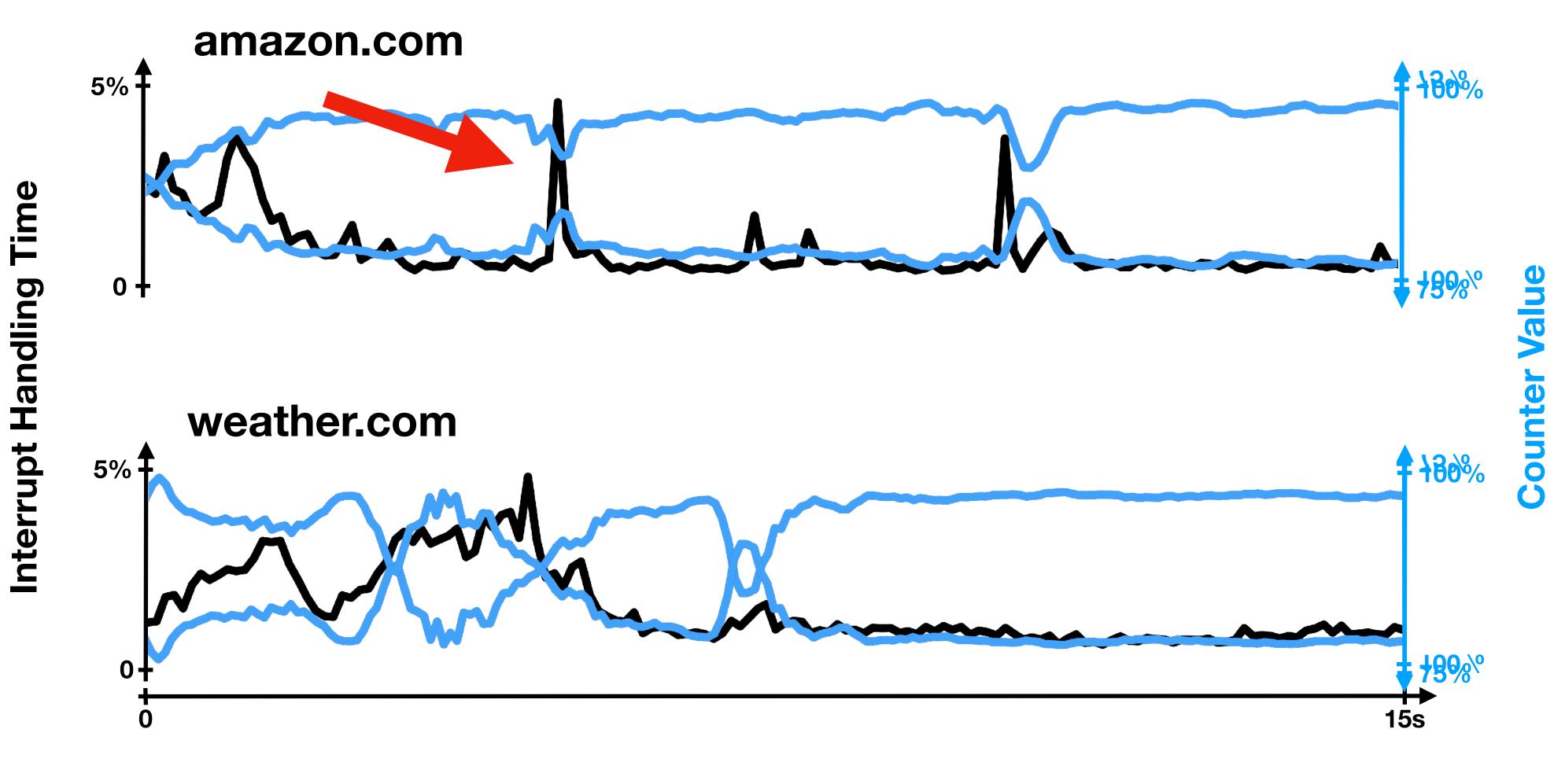

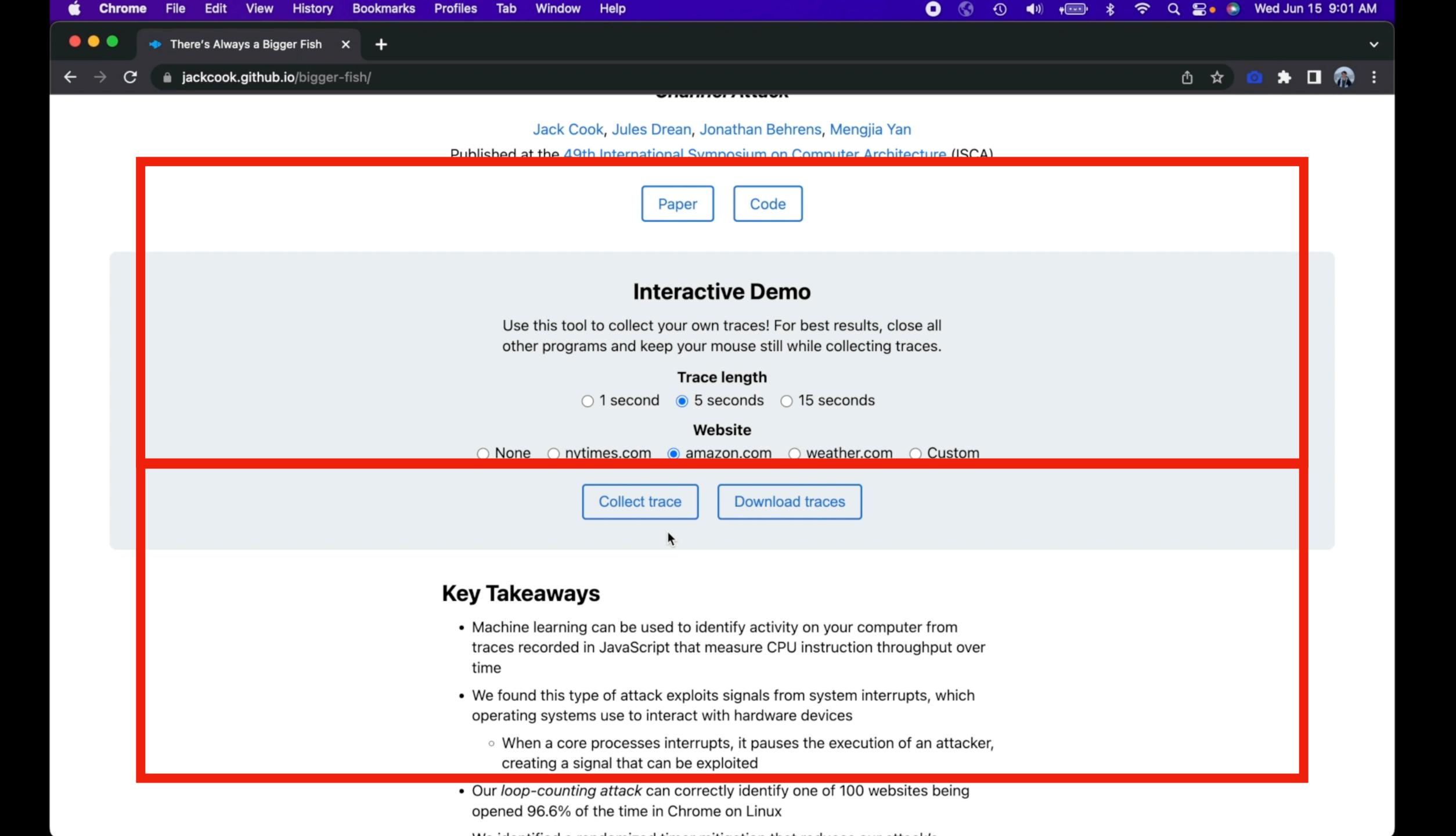

# A Cache-Occupancy Attack\*

#### ATTACKER'S CODE loop { start = time() counter = 0; while(time() - start < 5ms) {</pre> counter++; SWEEP\_CACHE(); Trace[start] = counter;

<sup>\*</sup> Shusterman, et al. "Prime+Probe 1,JavaScript 0: Overcoming Browser-based Side-Channel Defenses." USENIX Security'21

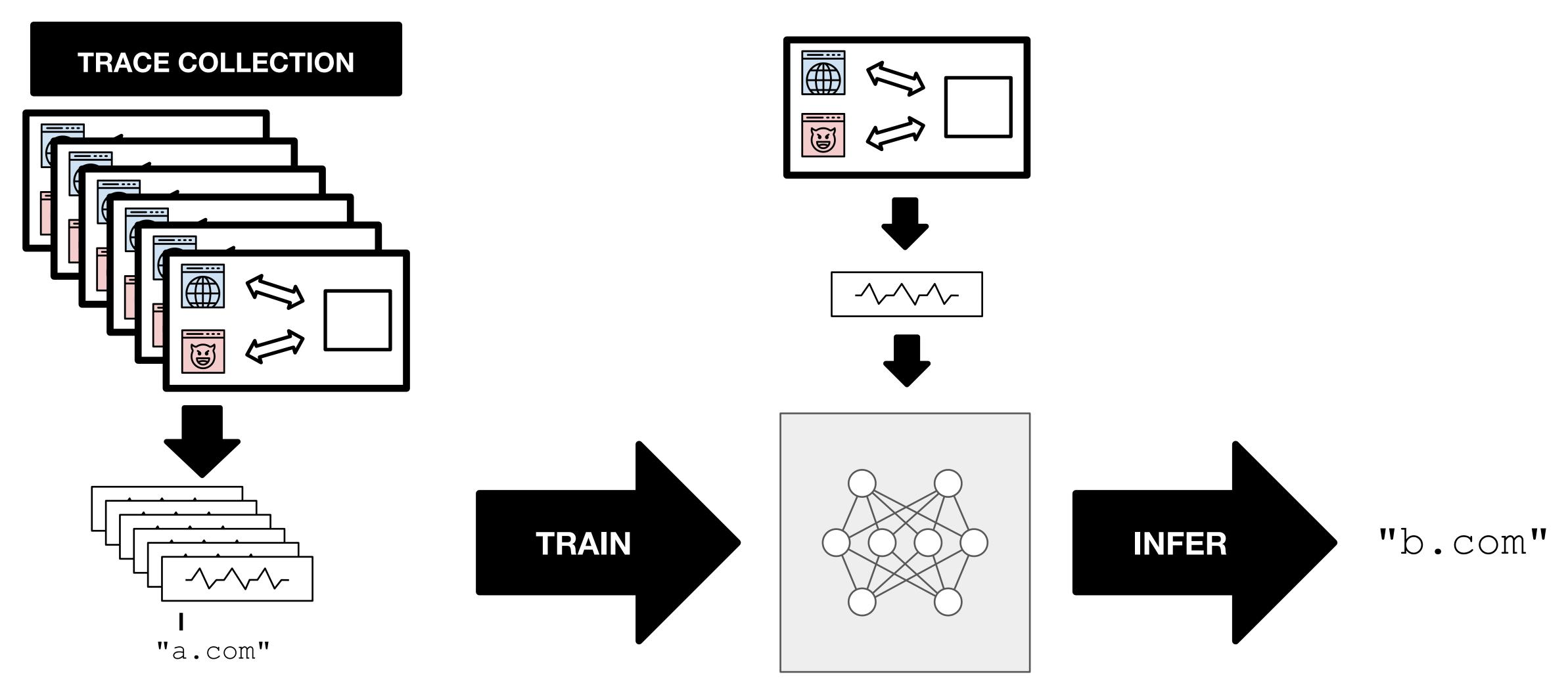

# Website Fingerprinting

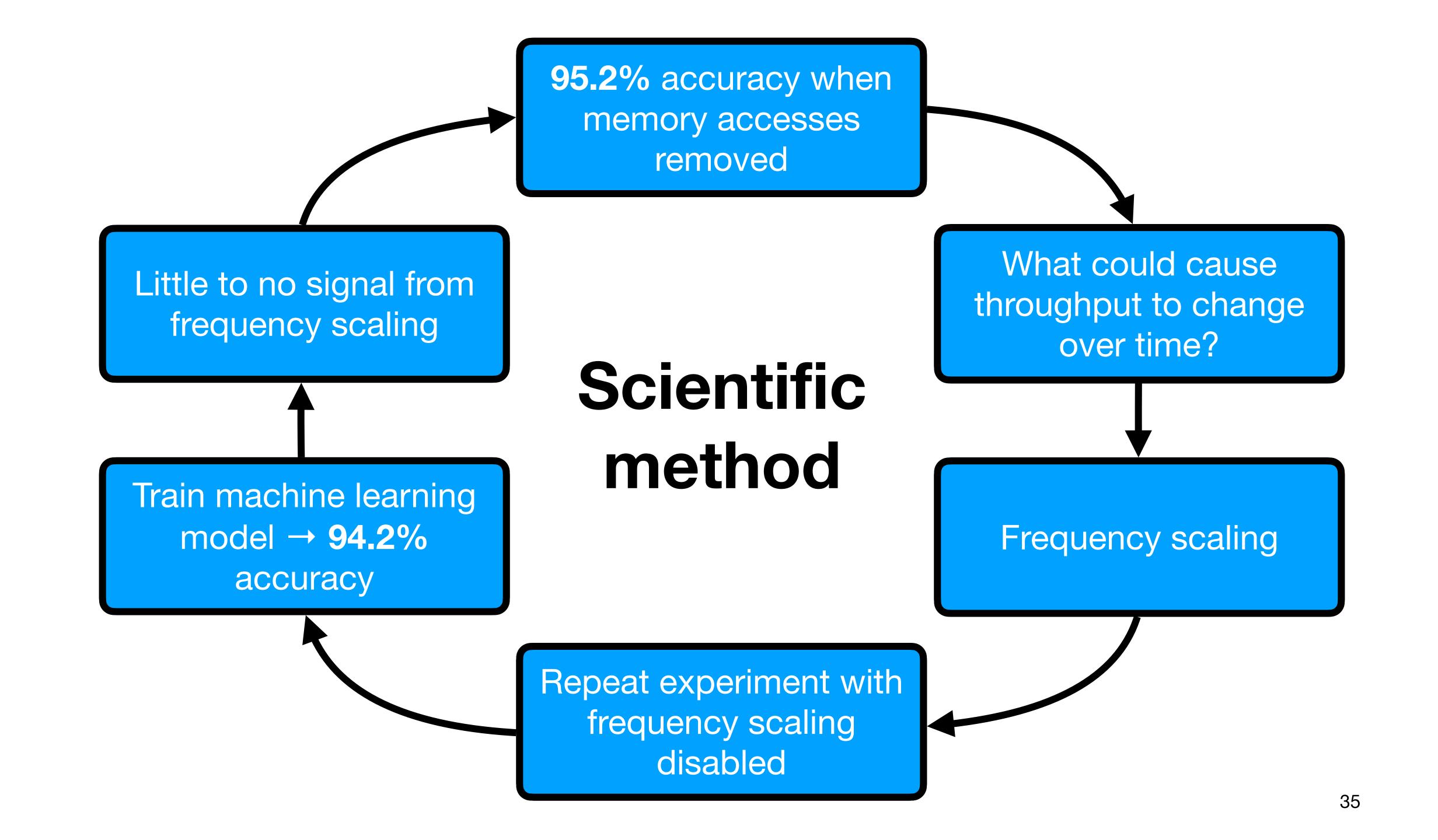

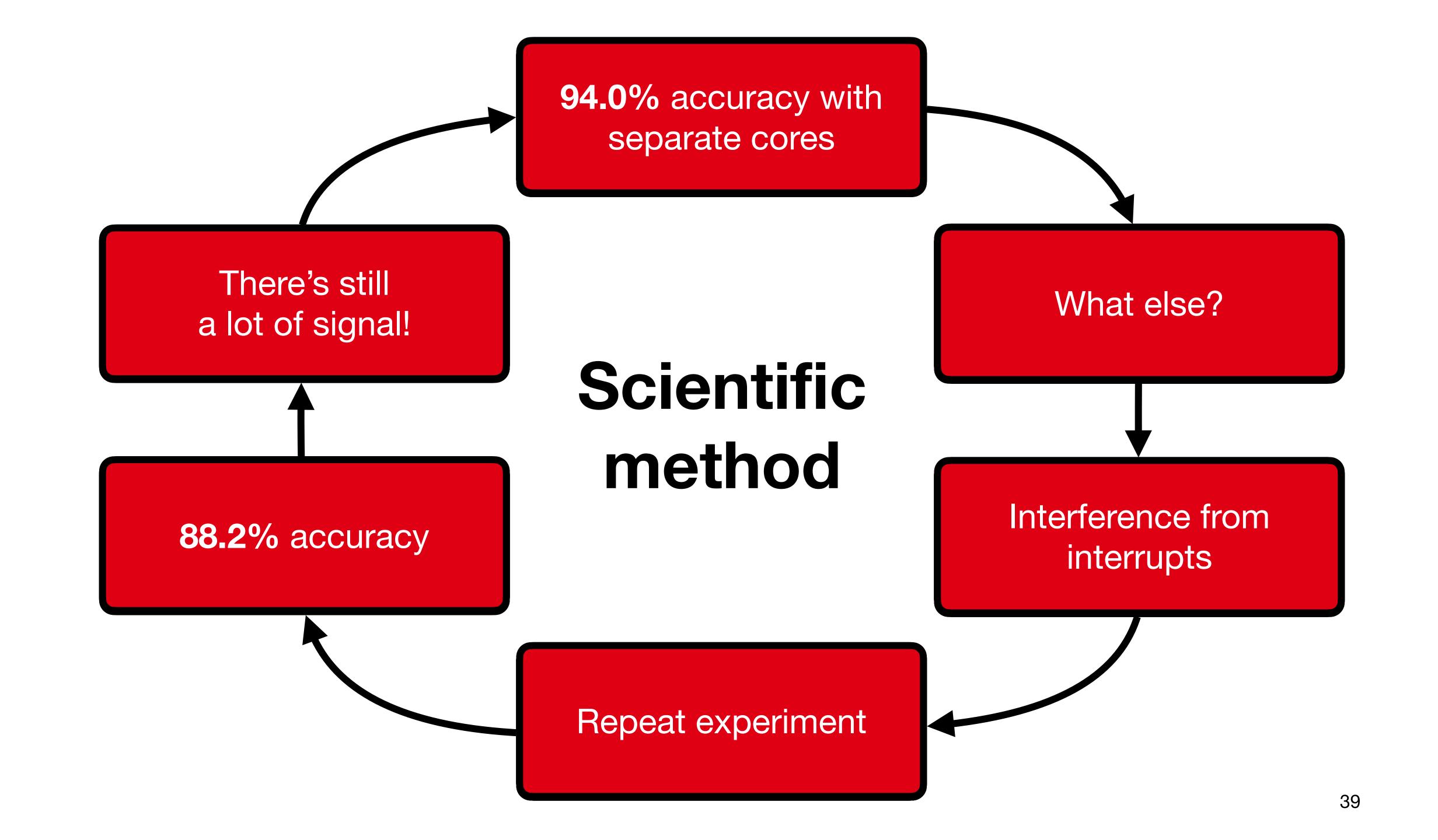

# A Surprising Experiment

```

ATTACKER'S CODE

loop {

start = time()

counter = 0;

while(time() - start < 5ms) {</pre>

counter++;

REMOVE MEMORY ACCESSES

Trace[start] = counter;

```

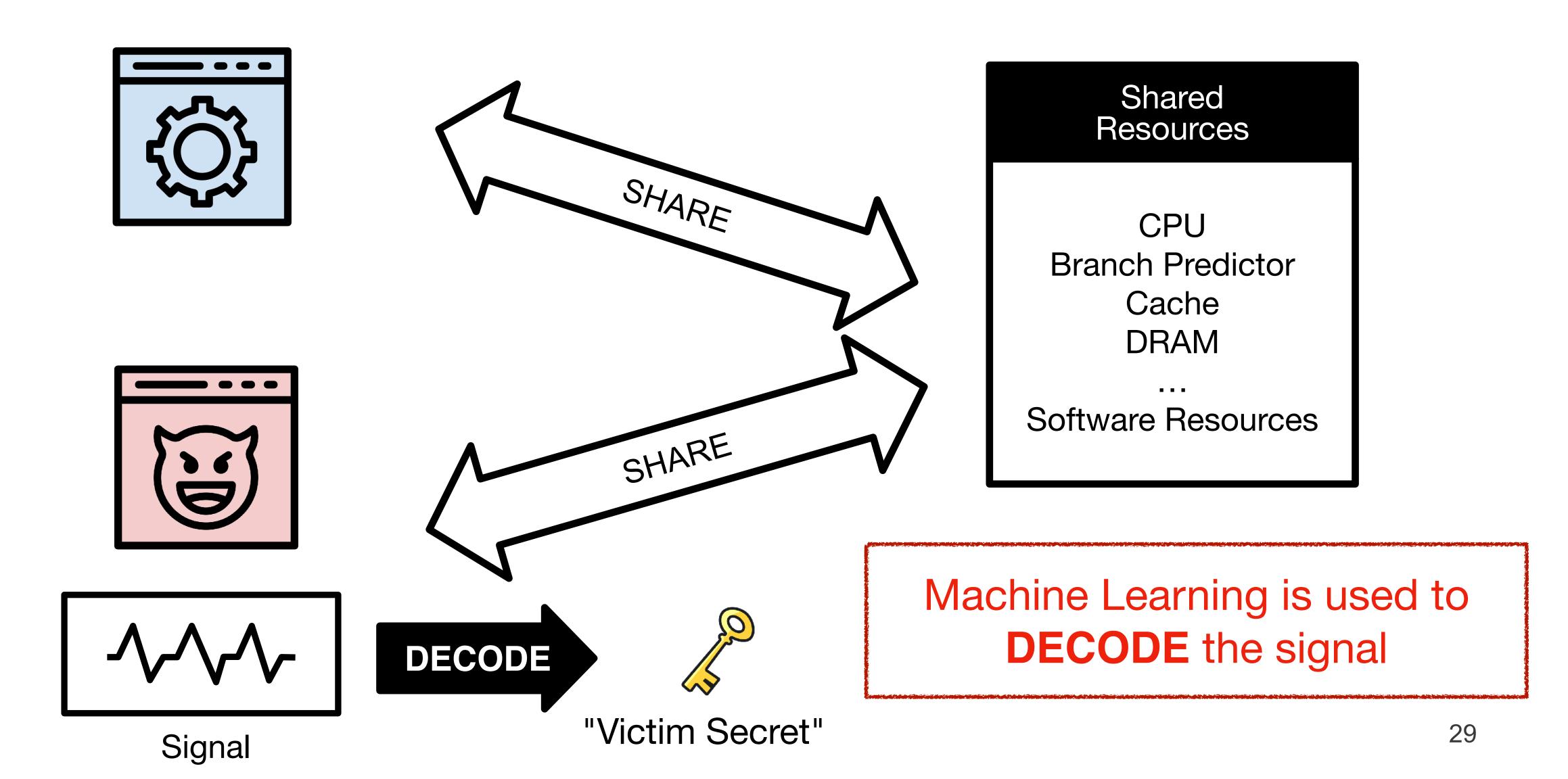

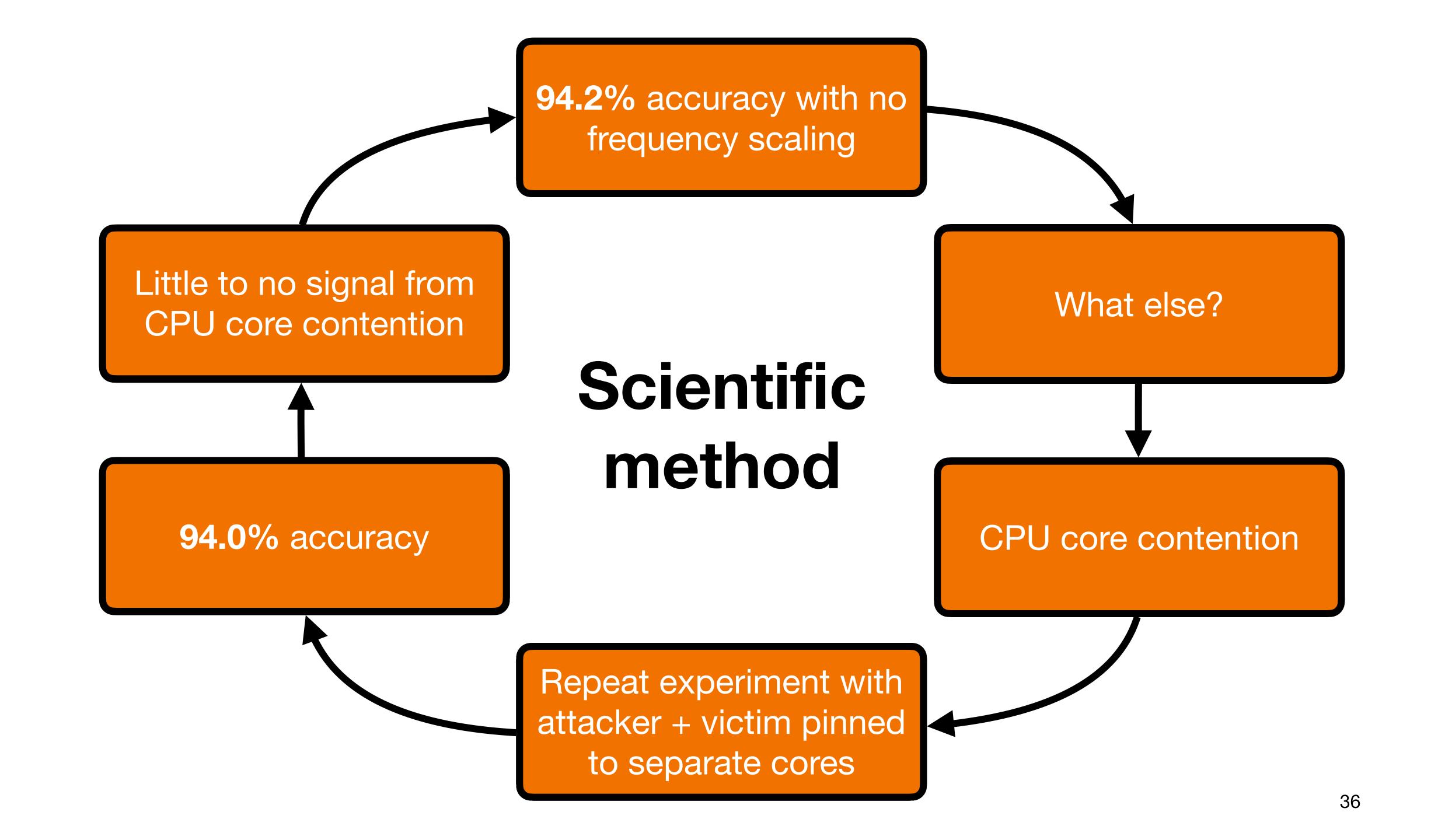

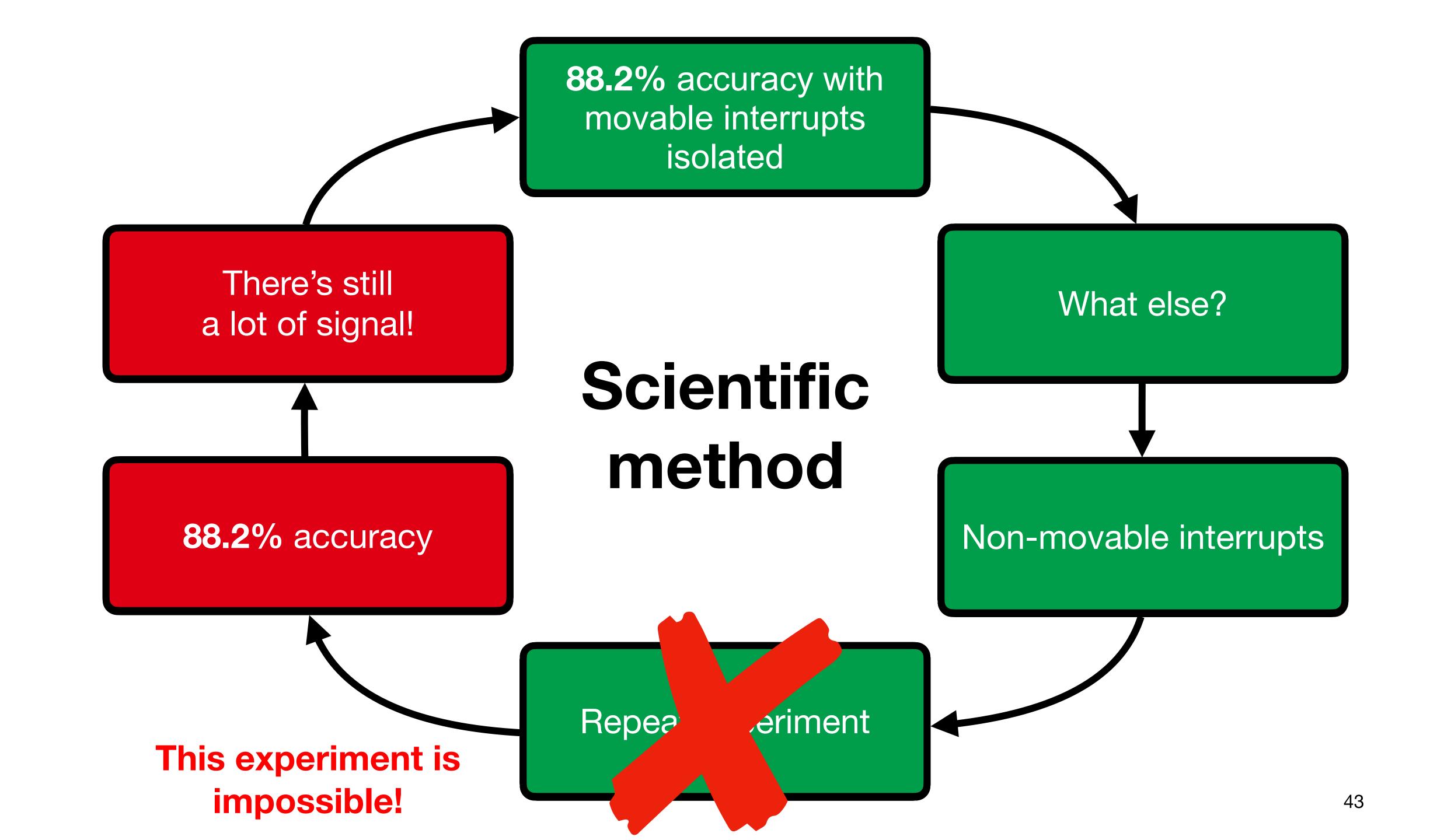

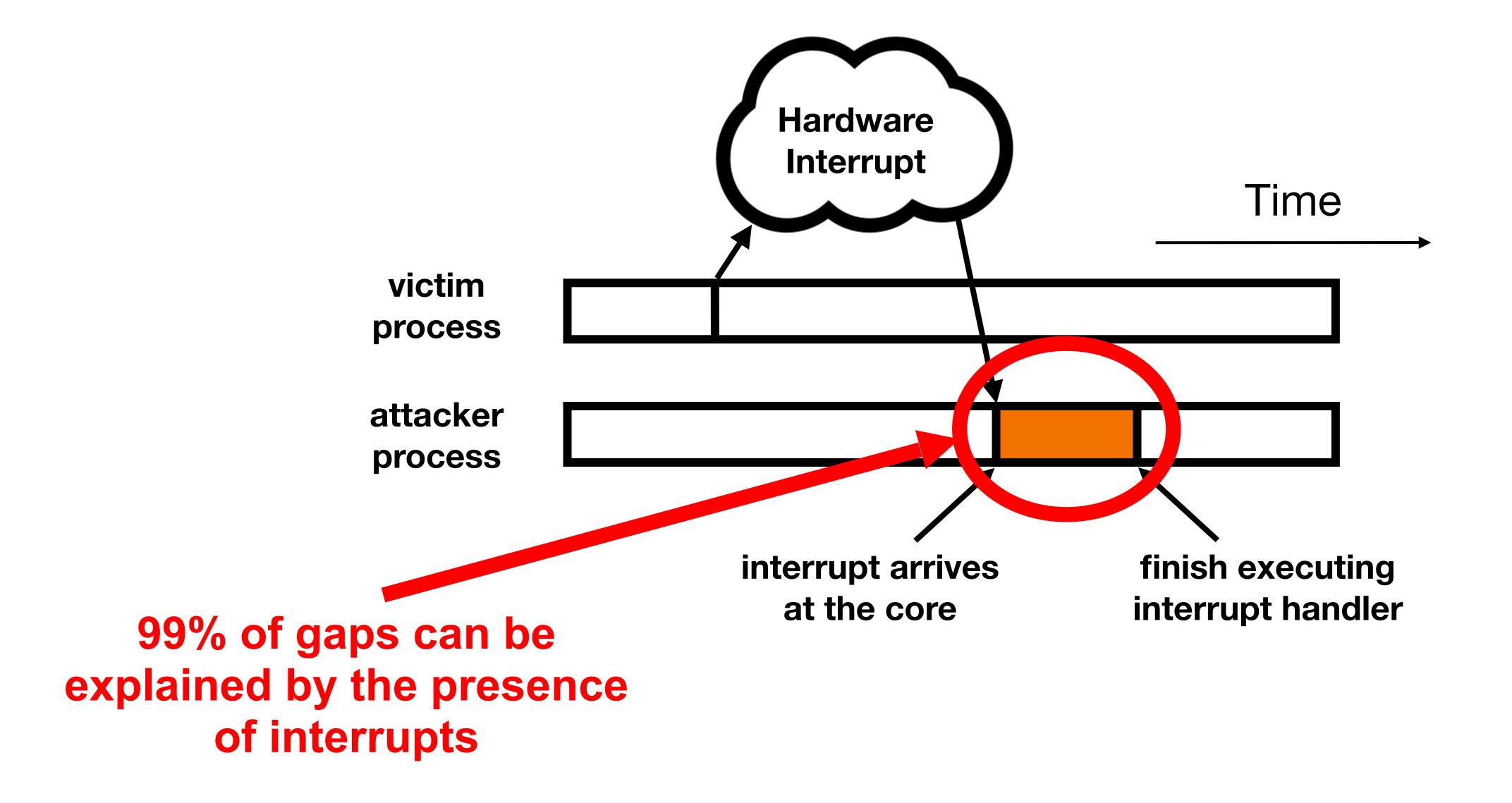

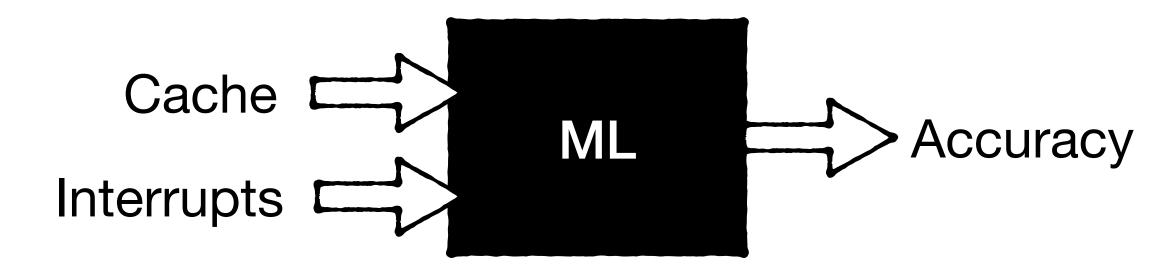

# What Is The Primary Side Channel?

ML-assisted side-channel attacks work as a black box.

It is challenging to find the root cause(s).

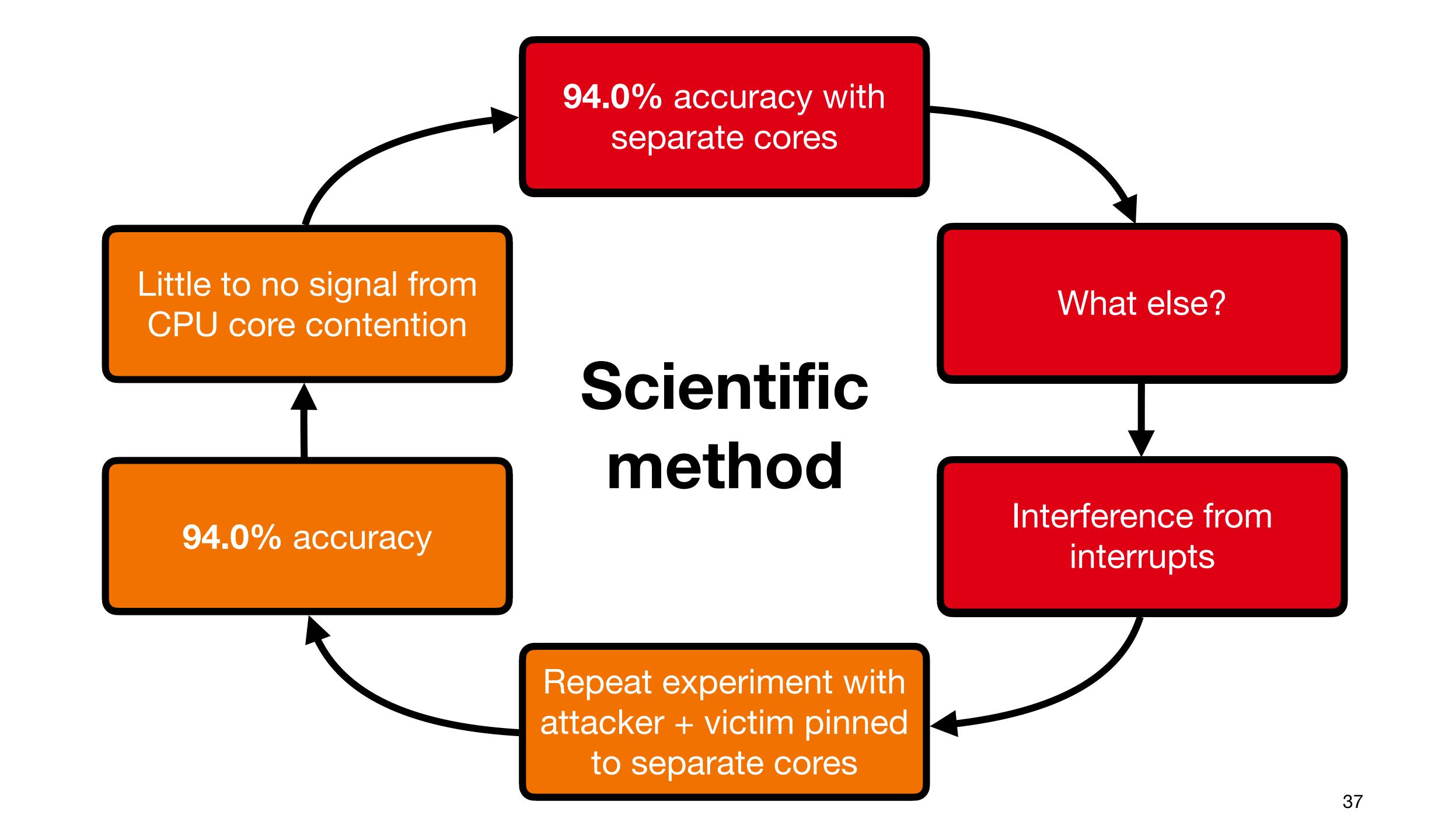

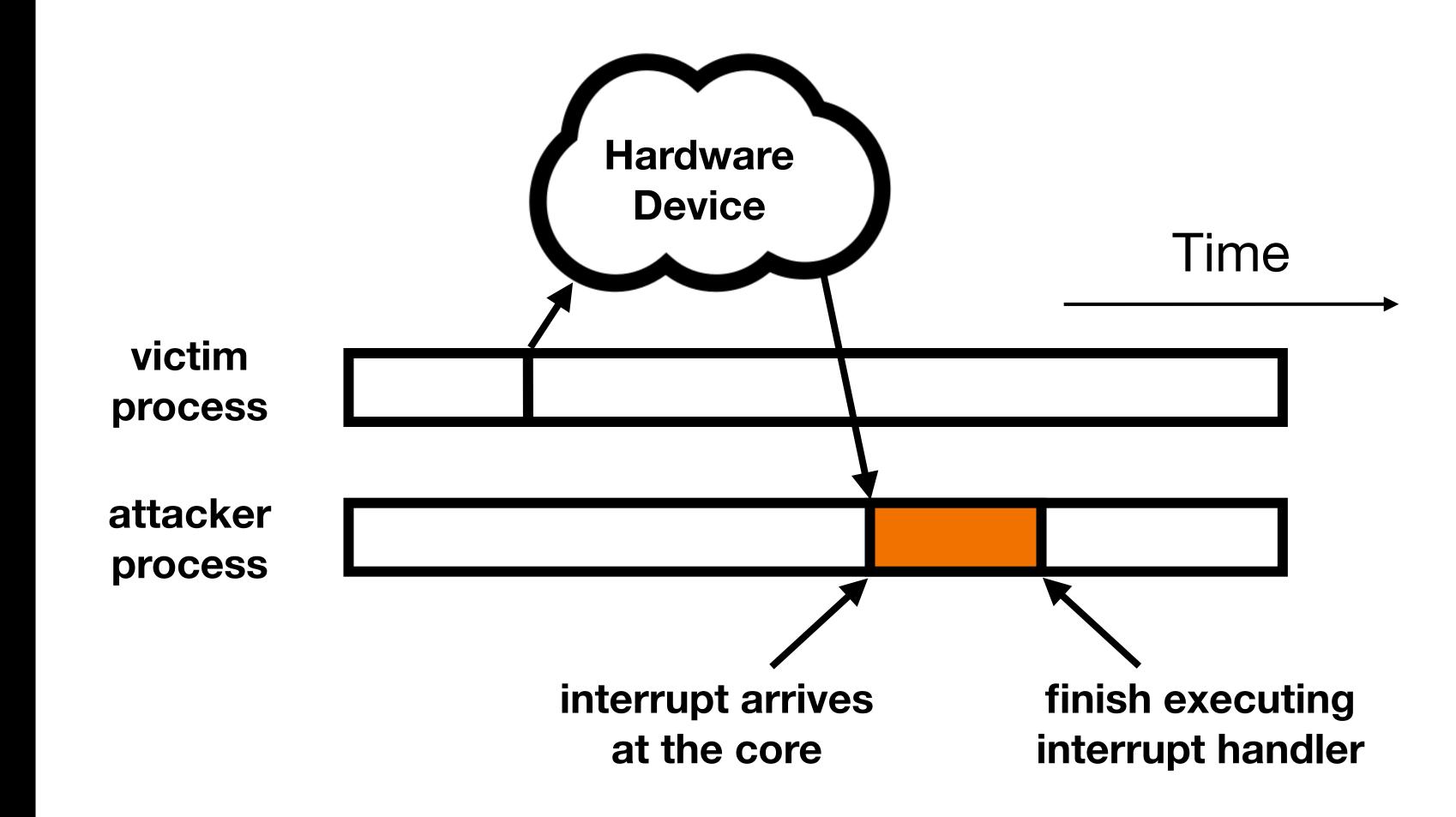

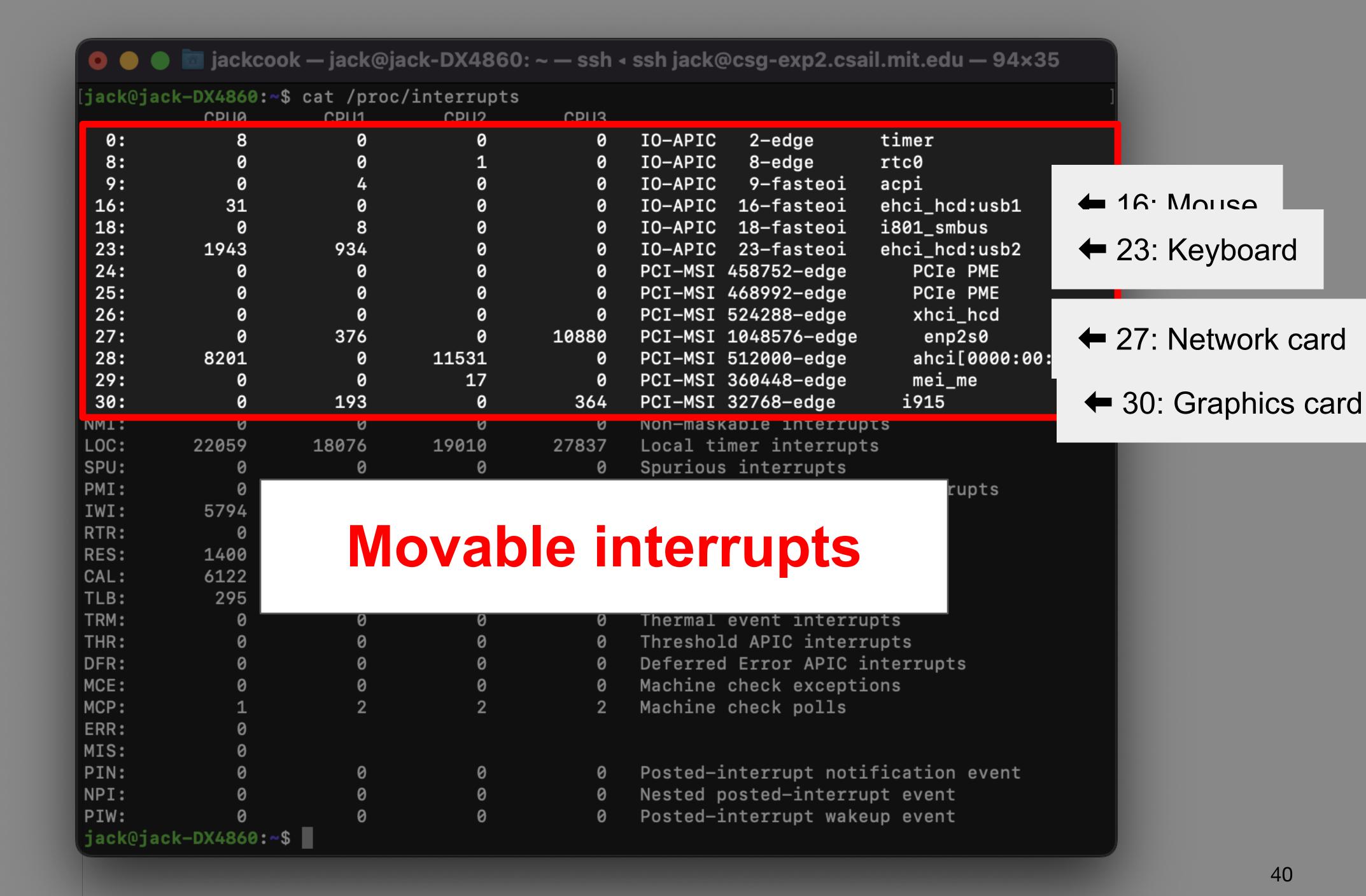

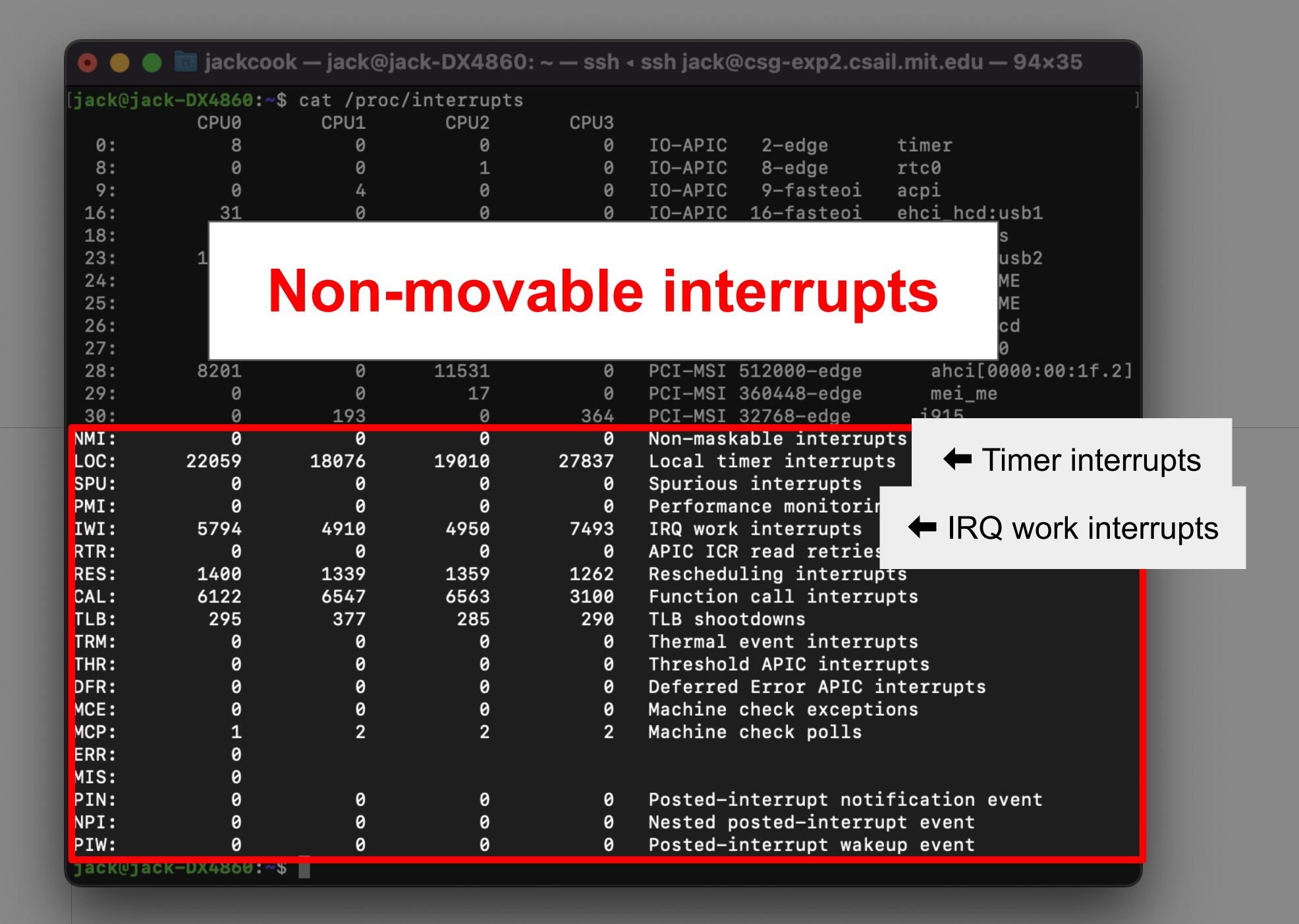

# System Interrupts

- Used to deal with asynchronous events

- e.g. Graphics interrupts render content on a display

- Some can be "pinned" to specific cores, some can't

### Non-Movable Interrupts

- Can't be isolated from any cores

- Are necessary for the operating system to function

- Have not been studied in detail for side channels

### System Instrumentation

In the kernel space: use eBPF

- Allows instrumentation of the Linux kernel at runtime

- We developed a tool to monitor interrupt characteristics by recording time at beginning and end of interrupt handlers

In the user space: attacker code in Rust

Records time leaves and re-enters the user space

####

**Time**

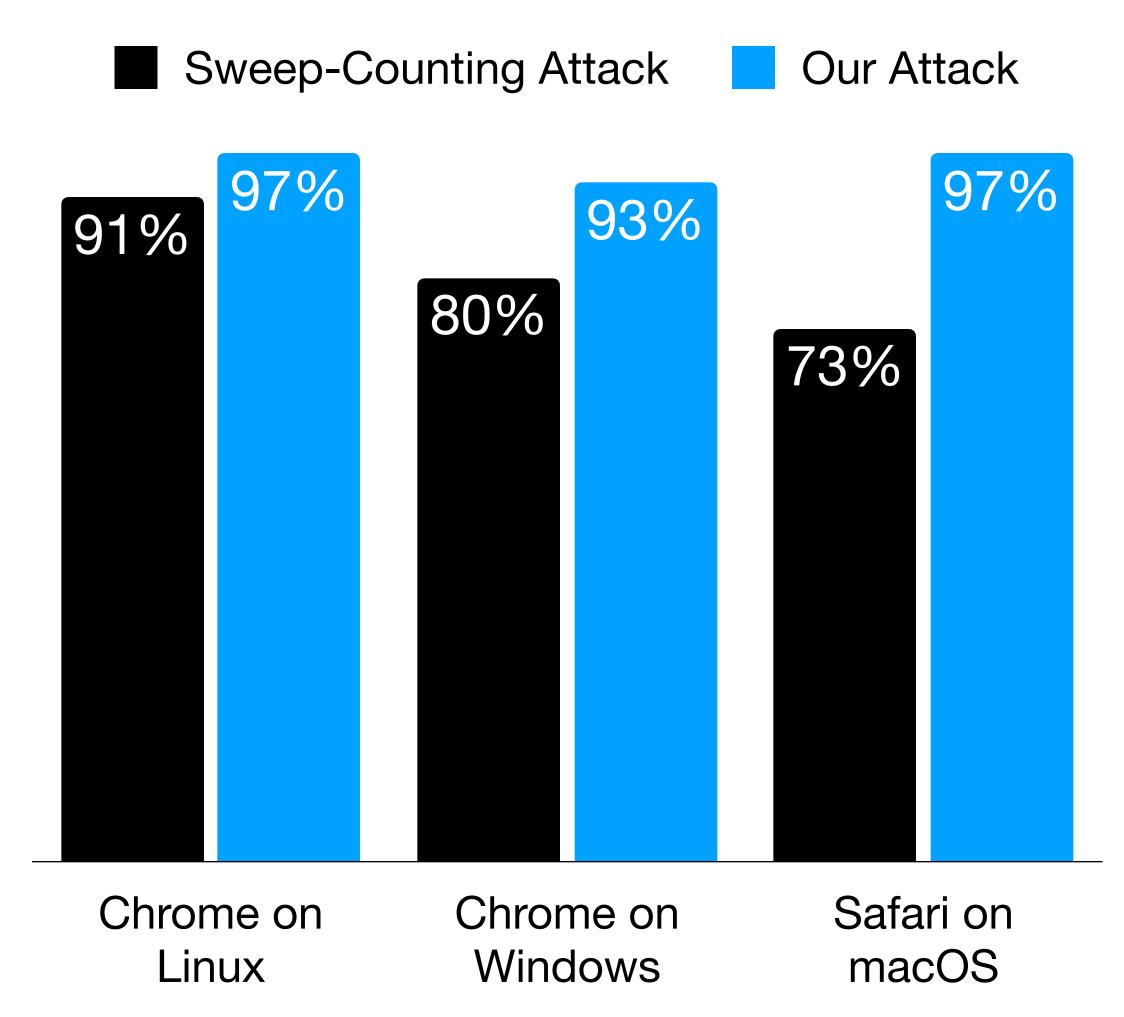

### Takeaway 2: There's always a bigger fish!

Need comprehensive security analysis in complex SW-HW systems

#### End of The Story?

- Run in separate VMs with interrupts pinned properly

- 88.2% → 91.6%

How to decipher signals from the ML model output?

A "bigger bigger" fish?

### Looking Beyond Microarchitectural-Only Side Channels

Takeaway 1: New threats arising from compound threat models

Takeaway 2: Need comprehensive security analysis for complex SW-HW systems

# Learning Computer Architecture Security For Fun — 5 Lab Assignments

#### The Team

Peter Deutsch

Jules Drean

Yuheng Yang

Shixin Song

Joseph Ravichandran

Jack Cook

Mengyuan Li

Miguel Gomez-Garcia

# Looking Beyond Microarchitectural-Only Side Channels